## Chapter.5

# **Transistor Bias Circuits**

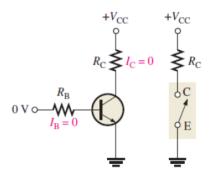

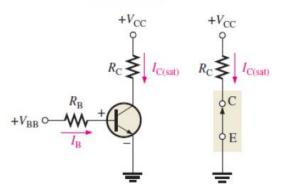

#### BJT as a Switch

#### (a) Cutoff - open switch

#### (b) Saturation - closed switch

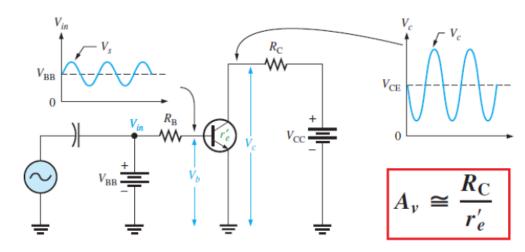

#### BJT as an Amplifier

### **DC Bias**

- ☐ A transistor must be properly biased with a dc voltage in order to operate as a linear amplifier.

- The purpose of biasing a circuit is to establish a proper stable dc operating point Q-point  $(V_{CE}, I_C)$ .

- A dc operating point must be set so that signal variations at the input terminal are amplified and accurately reproduced at the output terminal.

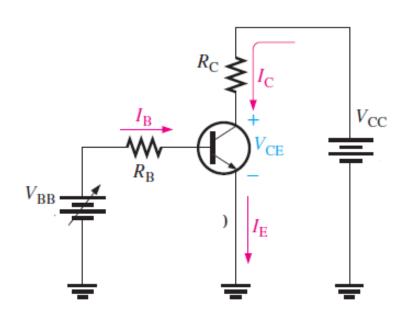

#### DC biased circuit

## **Graphical Analysis of DC Biasing**

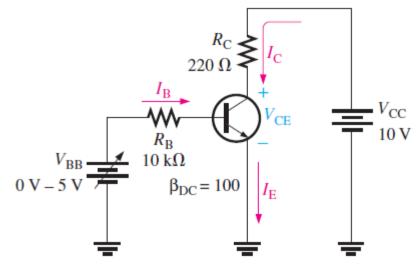

- The transistor is biased with  $V_{CC}$  and  $V_{BB}$  to obtain certain values of  $I_B$ ,  $I_C$ ,  $I_E$ , and  $V_{CE}$ .

- The **collector characteristic curves** are shown to illustrate the effects of dc bias.

- $\square$  By varying  $I_B$ , we can obtain several Q-points.

- **DC load line** passes through the Q-point on a transistor's collector curves intersecting the vertical axis at approximately  $\mathbf{I}_{\mathbf{C(sat)}}$  and the horizontal axis at  $\mathbf{V}_{\mathbf{CE(off)}}$ .

$$I_{C(sat)} = V_{CC} - V_{CE(sat)} / R_C = 45.5 \text{ mA}$$

(a) DC biased circuit

|                                                           | I <sub>B</sub> (μΑ) | I <sub>c</sub> (mA) | V <sub>CE</sub> (V)                            |

|-----------------------------------------------------------|---------------------|---------------------|------------------------------------------------|

| $Q_1$                                                     | 200                 | 20                  | 5.6                                            |

| $I_{\rm C}$ (mA) $Q_2$                                    | 300                 | 30                  | 3.4                                            |

| 60 - Q <sub>3</sub>                                       | 400                 | 40                  | 1.2                                            |

| $I_{\rm B} = 400 \mu{\rm A}$ $I_{\rm B} = 300 \mu{\rm A}$ |                     |                     |                                                |

| 20                                                        |                     | $I_{\rm B} = 20$    | 00 μΑ                                          |

| 0 1 2 3 4 5 6                                             | 7 8                 |                     | $I_{\text{CBO}} \cong 0$<br>$V_{\text{CE}}(V)$ |

(b) The dc load line.

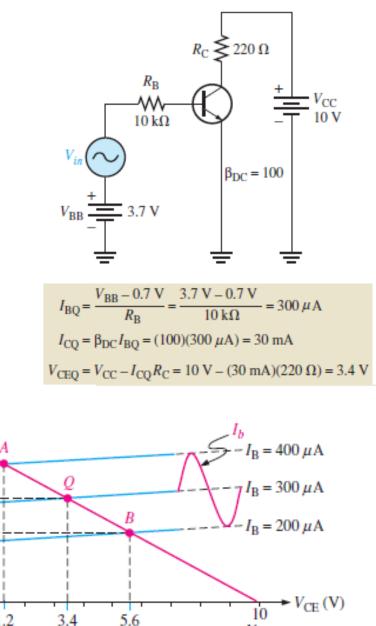

## **Linear Operation**

- The region along the load line including all points between saturation and cutoff is generally known as the **linear region** of the transistor's operation.

- ☐ The output voltage is ideally a linear reproduction of the input.

- **Q-Point**:  $(V_{CEQ} = 3.4 \text{ V}, I_{CQ} = 30 \text{ mA})$

- Assume sinusoidal voltage,  $V_{IN}$ , is superimposed on  $V_{BB}$ , causing the base current to vary sinusoidally 100  $\mu A$  above and below its Q-point value of 300  $\mu A$ .

- This causes the collector current to vary **10 mA** above and below its Q-point value of **30 mA**.

- The collector to-emitter voltage varies **2.2** V above and below its Q-point value of **3.4** V.

$V_{\rm CC}$

4

$I_{\rm C}$  (mA)

50 -45.5

-20

10

$V_{CEQ}$