## **Experiments in Digital Technology**

**1st Edition**

## © hps SystemTechnik

Lehr- + Lernmittel GmbH Altdorfer Strasse 16 88276 Berg / Germany

Phone: + 49 751 / 5 60 75 80 Telefax: + 49 751 / 5 60 75 17

Internet: http://www.hps-systemtechnik.com E-mail: export@hps-systemtechnik.com

Order no.: V 0160

All rights reserved. No part of this publication may be reproduced, transmitted, stored in a retrieval system, nor translated into any human or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior permission of hps SystemTechnik.

#### **Foreword**

Teaching in the field of "Digital Technology" can be conducted for the most part with practical methods in experiment classes.

This manual "Experiments in Digital Technology" offers, in concise form, all the teaching material which needs to be covered in basic and further training courses following the reorganisation of the electrical engineering vocations. Some of the experiments progress beyond the actual syllabus of vocational training colleges in part (e. g. experiments with the ALU and other components) so that they are also suitable for pupils at technical schools or electrotechnical courses at technical grammar schools.

The manual contains experiments with different degrees of difficulty for all the subjects offered to provide teachers with a reasonable choice.

In addition, the Digital Training System offers the teacher the possibility of adding his own experiments to the individual subject fields in order to select the right emphasis of content for his class. The instructions have been compiled in such a way that, on the one hand, the pupil can be taught new knowledge and skills step by step, whereby independent planning, execution and evaluation of the experiments is aimed at, and on the other hand already available knowledge can be deepended and consolidated.

The chapter **Fundamental principles** contains an introduction to the respective subject.

The appropriate **Experiments section** contains the tasks and notes on their execution. Circuits, tables and diagrams are often provided in part to save the pupil time-consuming writing.

There is a detailed **Solutions section** at the back of the book with the answers to the set taks and questions to allow the student to check his own work.

Notes:

## **List of Contents**

| Forev | vora 1                                                             |

|-------|--------------------------------------------------------------------|

| 1.    | Basic logic circuits 3                                             |

| 1.1   | Fundamental principles                                             |

| 1.1.1 | Forms of representation and aids 3                                 |

| 1.1.2 | Laws of switching algebra 5                                        |

| 1.1.3 | Complete disjunctive normal form 6                                 |

| 1.1.4 | Complete conjunctive normal form 6                                 |

| 1.1.5 | KV diagrams 7                                                      |

| 1.1.6 | Logic functions with NOR and NAND elements                         |

| 1.2   | Experiments section 9                                              |

| 1.2.1 | Important binary logic operations 9                                |

| 1.2.2 | Laws of switching algebra 10                                       |

| 1.2.3 | Disjunctive and conjunctive normal form 15                         |

| 1.2.4 | Circuit design with the aid of KV diagrams                         |

| 1.2.5 | Representation of switching networks in NAND and NOR technology 19 |

| 1.2.6 | Equivalence                                                        |

| 1.2.7 | Antivalence                                                        |

| 1.2.8 | Working with TTL components 24                                     |

| 2.    | Schmitt triggers 27                                                |

| 2.1   | Fundamental principles 27                                          |

| 2.2   | Experiments section                                                |

| 3.                        | Bistable multivibrators                                                | 29                              |

|---------------------------|------------------------------------------------------------------------|---------------------------------|

| 3.1                       | Fundamental principles                                                 | 29                              |

| 3.1.1                     | General                                                                | 29                              |

| 3.1.2                     | Asynchronous flipflops                                                 | 29                              |

| 3.1.3                     | Synchronous flipflops                                                  | 31                              |

| 3.2                       | Experiments section                                                    | 33                              |

| 3.2.1                     | RS flipflop consisting of NOR gates                                    | 33                              |

| 3.2.2                     | RS flipflop consisting of NAND gates                                   | 34                              |

| 3.2.3                     | Clock state controlled RS flipflops                                    | 35                              |

| 3.2.4                     | RS flipflops with dominant S or R input                                | 36                              |

| 3.2.5                     | D flipflops                                                            | 37                              |

| 3.2.6                     | Single edge controlled RS flipflop                                     | 38                              |

| 3.2.7                     | Two state controlled D flipflop                                        | 41                              |

|                           |                                                                        |                                 |

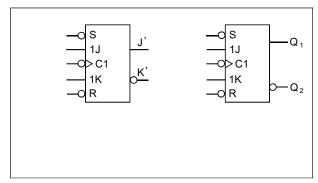

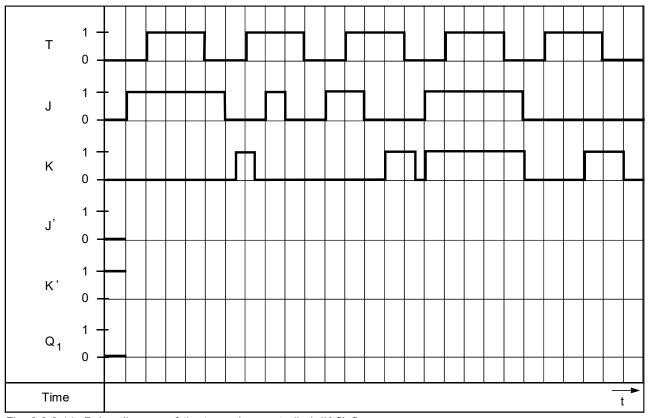

| 3.2.8                     | Single edge controlled JK flipflop                                     | 42                              |

| 3.2.8                     | Single edge controlled JK flipflop                                     | 42                              |

| 3.2.8<br><b>4.</b>        | Single edge controlled JK flipflop  Monostable multivibrators          |                                 |

|                           |                                                                        | 47                              |

| 4.                        | Monostable multivibrators                                              | 47<br>47                        |

| <b>4</b> .<br><b>4</b> .1 | Monostable multivibrators                                              | 47<br>47                        |

| 4.<br>4.1<br>4.2          | Monostable multivibrators                                              | 47<br>47<br>48                  |

| 4.<br>4.1<br>4.2          | Monostable multivibrators  Fundamental principles  Experiments section | 477<br>477<br>488               |

| <b>4. 4.1 4.2</b> 4.2.1   | Monostable multivibrators  Fundamental principles  Experiments section | 477<br>477<br>488               |

| <b>4. 4.1 4.2</b> 4.2.1   | Monostable multivibrators  Fundamental principles  Experiments section | 47<br>47<br>48<br>48<br>49      |

| 4. 4.1 4.2 4.2.1          | Monostable multivibrators  Fundamental principles  Experiments section | 477<br>478<br>488<br>489<br>533 |

| 4. 4.1 4.2 4.2.1 4.2.2    | Monostable multivibrators  Fundamental principles                      | 477<br>478<br>488<br>489<br>533 |

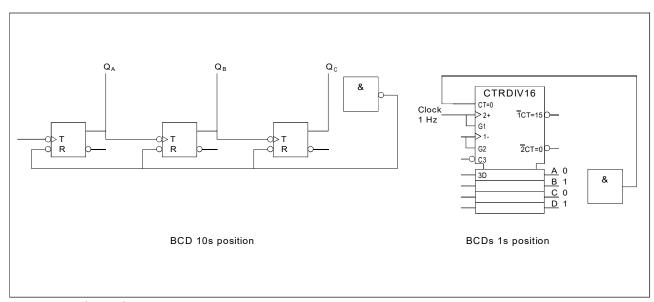

| 5.2   | Experiments section                     | 56 | 7.1.4  | Modulo-n counters 90                         |

|-------|-----------------------------------------|----|--------|----------------------------------------------|

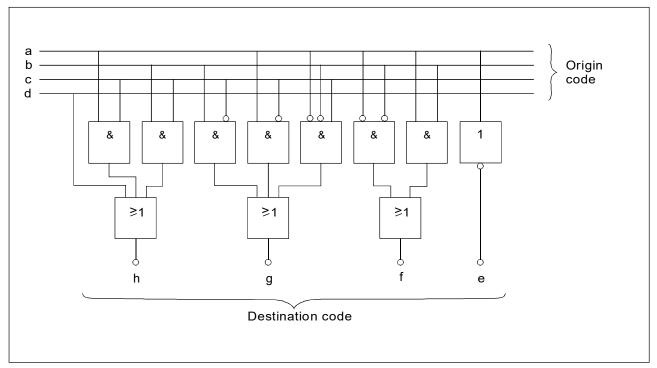

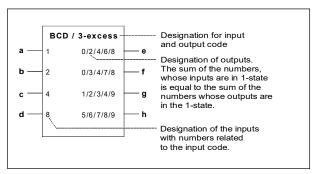

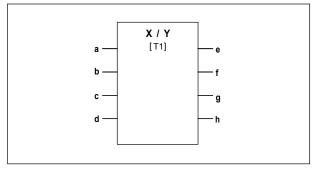

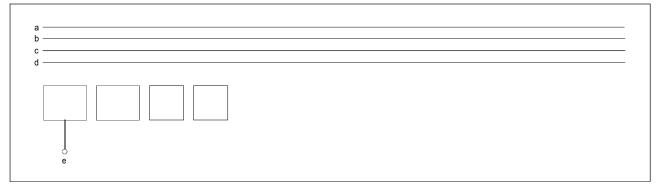

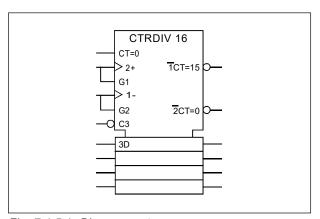

| 5.2.1 | 8421-BCD / Decimal code converter       | 56 | 7.1.5  | Programmable counters 91                     |

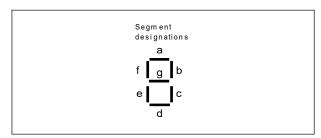

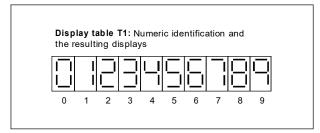

| 5.2.2 | 8421-BCD / 7-segment code converter     | 58 | 7.2    | Experiments section                          |

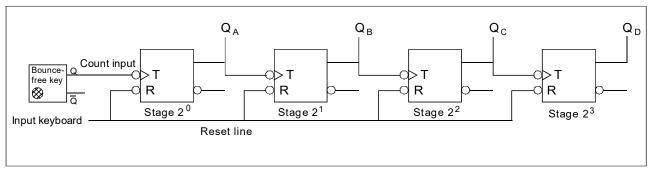

| 5.2.3 | Coding circuits                         | 61 | 7.2.1  | Asynchronous up counters 92                  |

|       |                                         |    | 7.2.2  | Asynchronous down counters 94                |

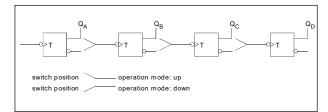

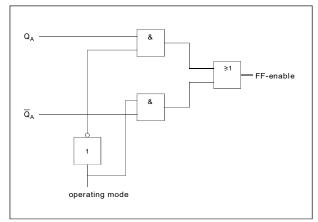

| 6.    | Arithmetic circuits                     | 63 | 7.2.3  | Asynchronous reversing counters 96           |

| 6.1   | Fundamental principles                  | 63 | 7.2.4  | Asynchronous modulo-n counters 97            |

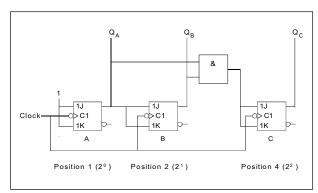

| 6.1.1 | General                                 | 63 | 7.2.5  | Synchronous counters                         |

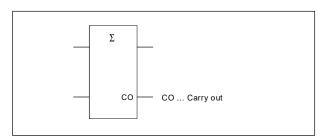

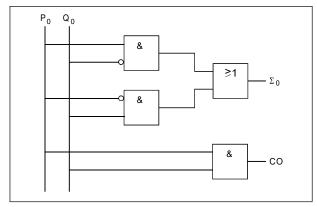

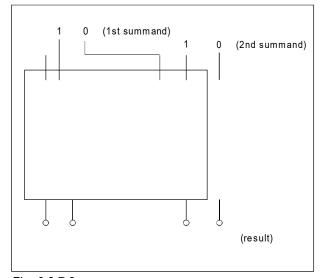

| 6.1.2 | Semi adder                              | 63 | 7.2.6  | Programmable counters                        |

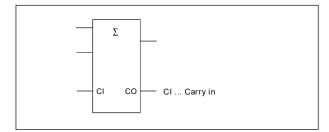

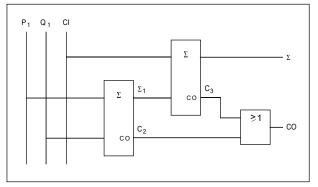

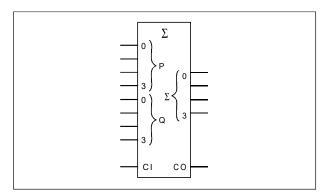

| 6.1.3 | Full adder                              | 64 |        |                                              |

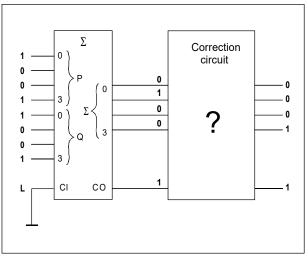

| 6.1.4 | Correction addition for decimal numbers | 65 | 8.     | Register circuits 105                        |

| 6.1.5 | Subtractor for dual numbers             | 66 | 8.1    | Fundamental principles                       |

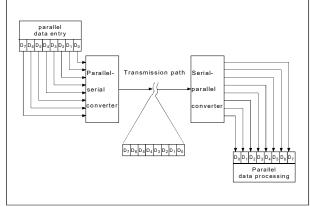

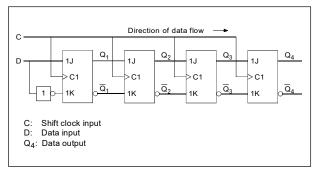

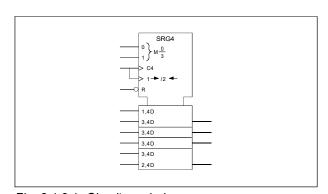

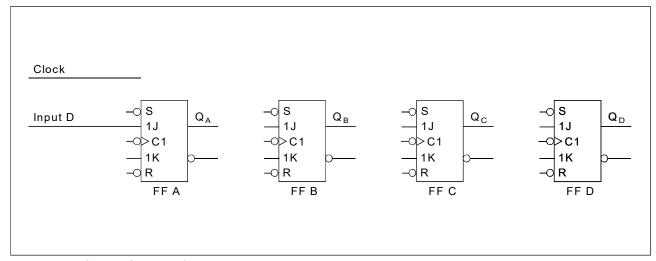

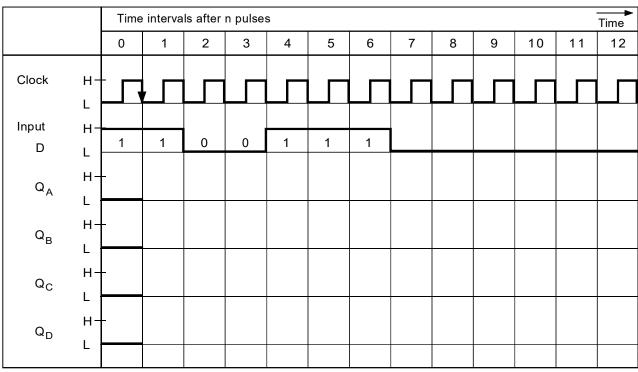

| 6.2   | Experiments section                     | 68 | 8.1.1  | General                                      |

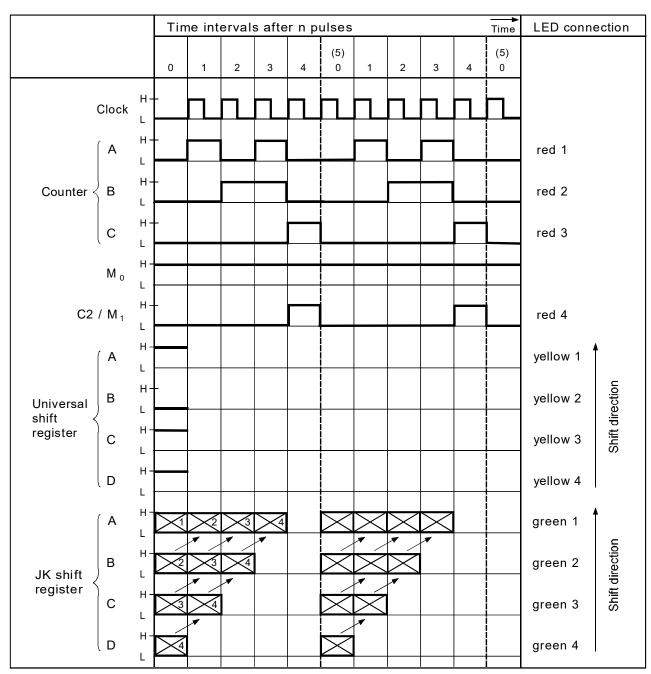

| 6.2.1 | Semi adder                              | 68 | 8.1.2  | Shift registers                              |

| 6.2.2 | Full adder                              | 70 | 8.1.3  | Universal shift registers 106                |

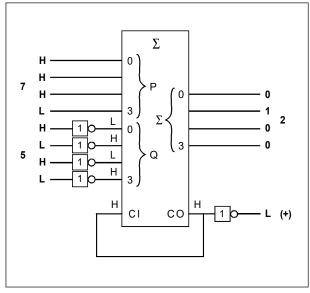

| 6.2.3 | Adding circuits for the 8421-BCD code   | 72 | 8.2    | Experiments section                          |

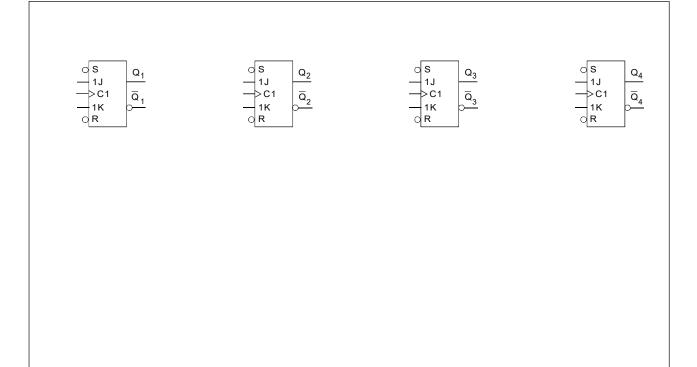

| 6.2.4 | Semi subtractor                         | 77 | 8.2.1  | JK shift registers                           |

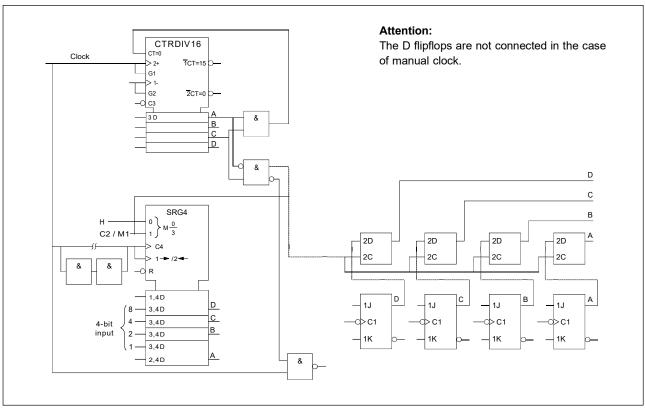

| 6.2.5 | Full subtractor                         | 78 | 8.2.2  | Shift registers with parallel data input 109 |

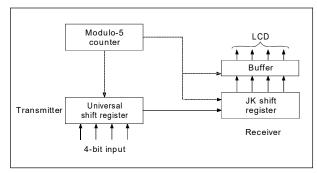

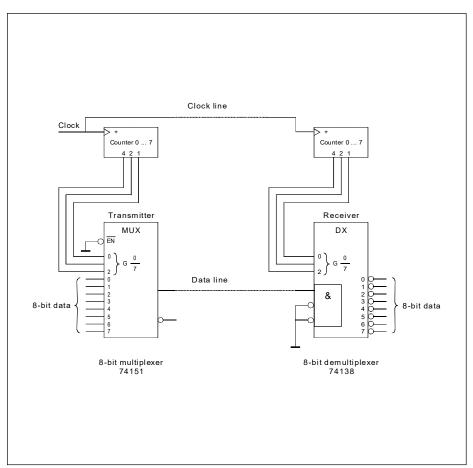

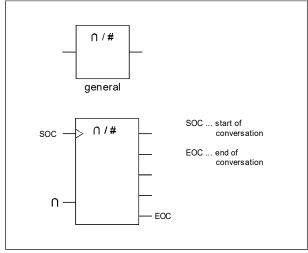

| 6.2.6 | Subtractor for dual numbers             | 81 | 8.2.3  | Serial data transfer                         |

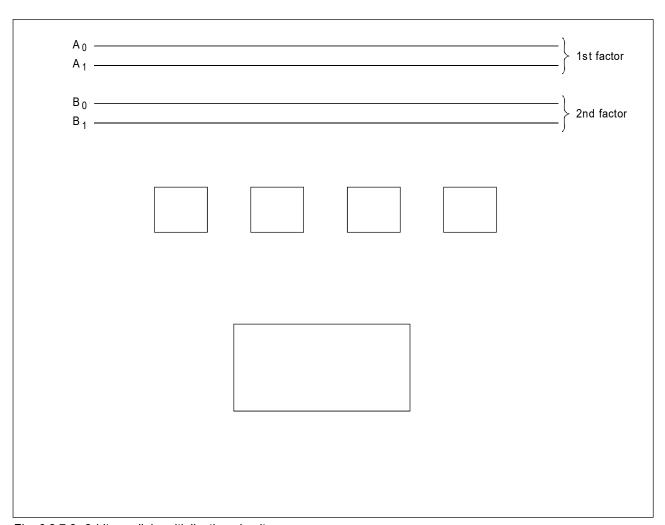

| 6.2.7 | 2-bit parallel multiplication circuit   | 83 |        |                                              |

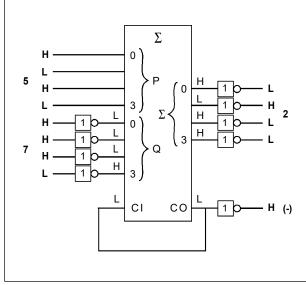

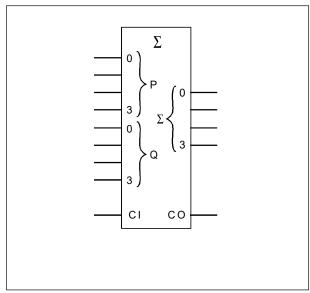

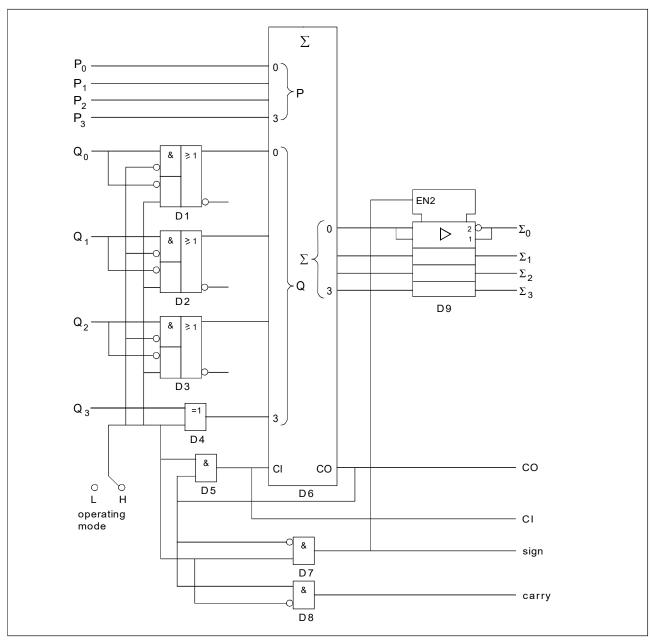

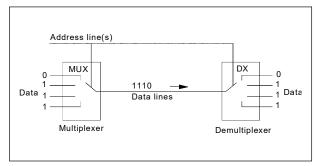

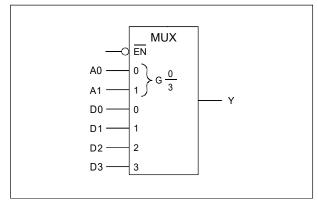

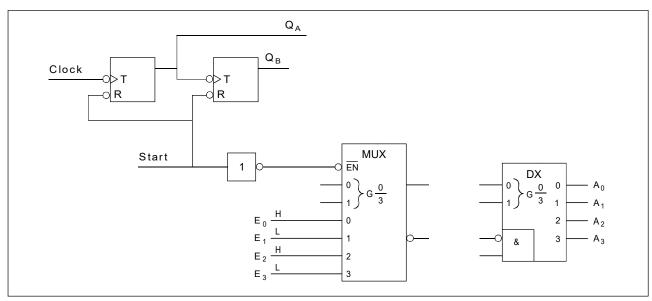

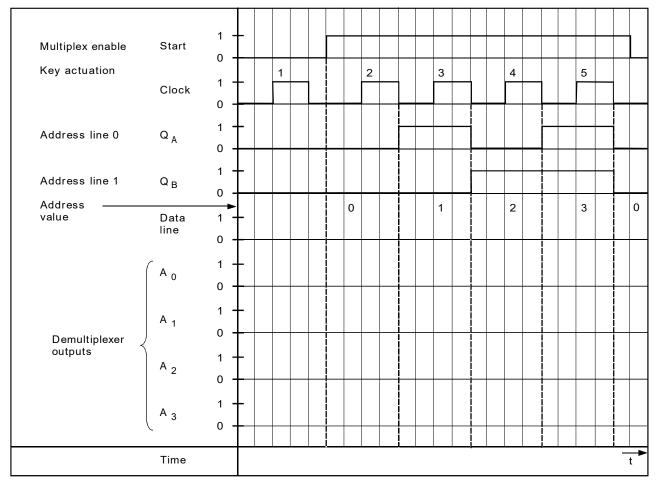

| 6.2.8 | Arithmetic unit for 4-bit dual numbers  | 85 | 9.     | Multiplex mode 115                           |

|       |                                         |    | 9.1    | Fundamental principles                       |

| 7.    | Counting circuits                       | 87 | 9.2    | Experiments section                          |

| 7.1   | Fundamental principles                  | 87 |        |                                              |

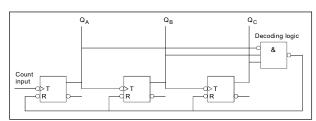

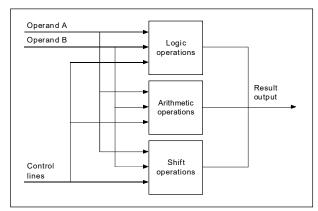

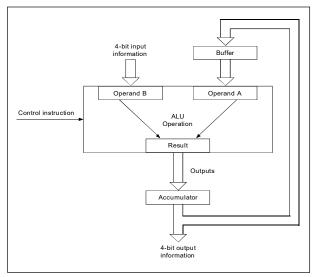

| 7.1.1 | General                                 | 87 | 10.    | Arithmetic logic unit 121                    |

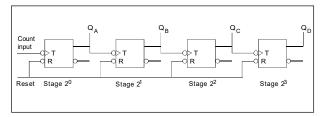

| 7.1.2 | Asynchronous counters                   | 87 | 10.1   | Fundamental principles 121                   |

| 7.1.3 | Synchronous counters                    | 88 | 10.1.1 | General                                      |

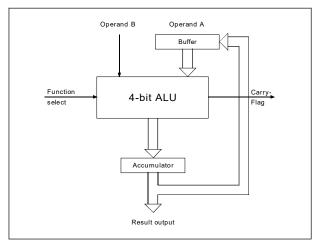

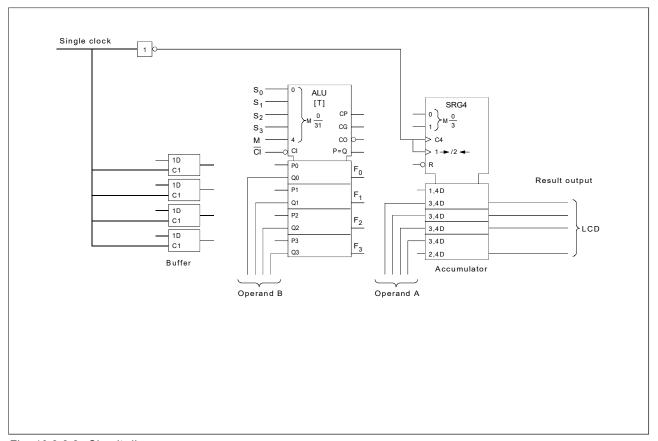

| 10.1.2 | Interaction of ALU and accumulator           | 121 |

|--------|----------------------------------------------|-----|

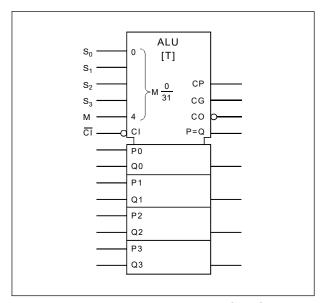

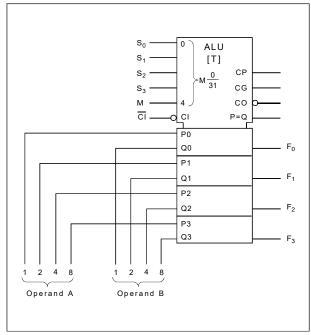

| 10.1.3 | Arithmetic logic unit 74HC/HCT181            | 122 |

| 10.2   | Experiments section                          | 124 |

| 10.2.1 | Arithmetic operations                        | 124 |

| 10.2.2 | ALU with accumulator                         | 126 |

|        |                                              |     |

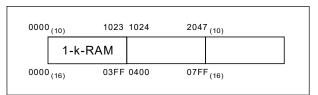

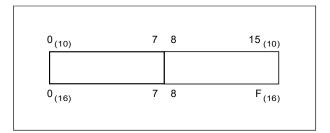

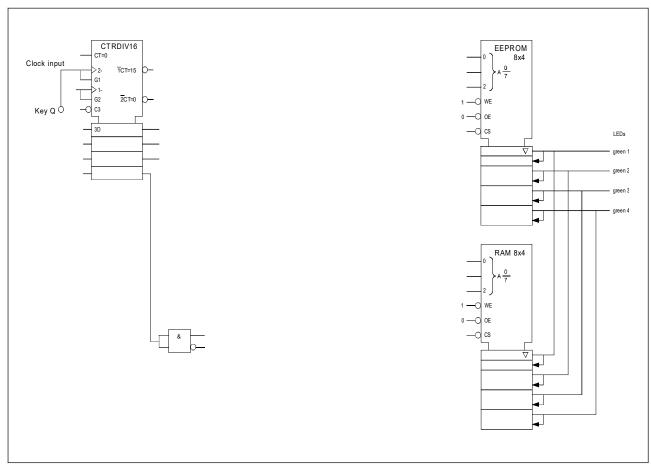

| 11.    | Memory circuits                              | 129 |

| 11.1   | Fundamental principles                       | 129 |

| 11.1.1 | General                                      | 129 |

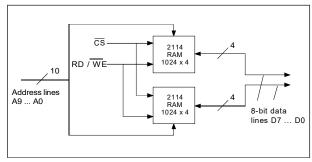

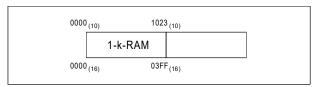

| 11.1.2 | Extension of the word width                  | 129 |

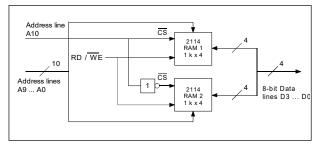

| 11.1.3 | Extension of the number of memory            |     |

|        | locations                                    | 130 |

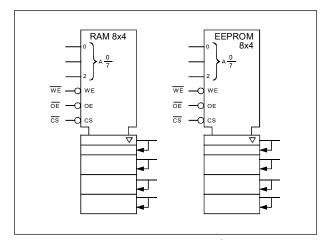

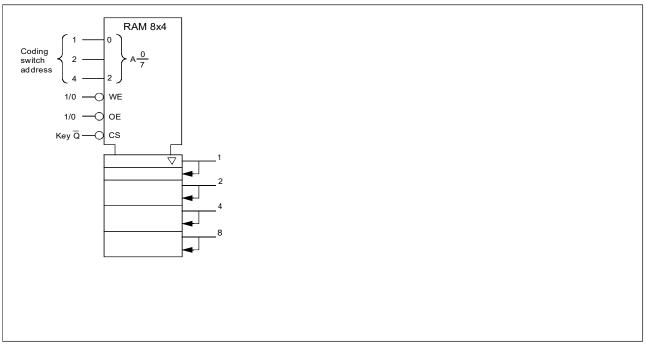

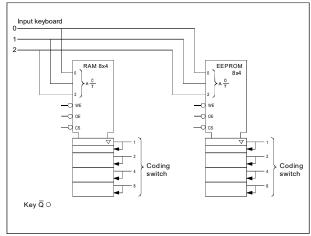

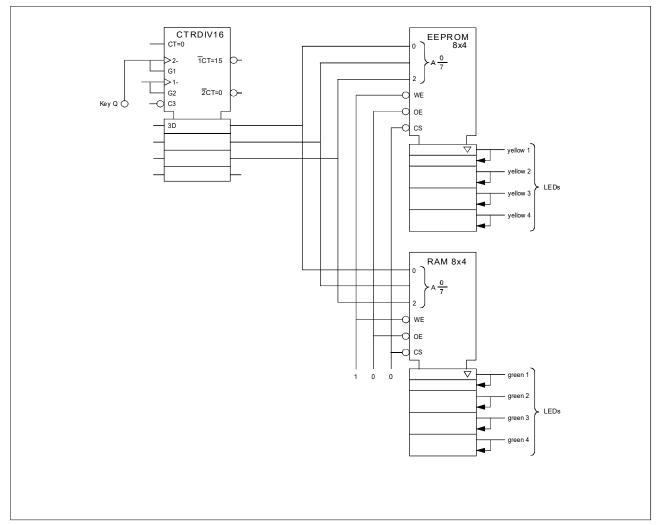

| 11.1.4 | Memory components RAM 8 x 4 and EEPROM 8 x 4 | 121 |

| 11 2   | Experiments section                          |     |

|        | Writing and reading memory                   | 102 |

|        | components                                   | 132 |

| 11.2.2 | Word width                                   | 134 |

| 11.2.3 | Memory capacity                              | 137 |

|        |                                              |     |

| 12.    | Analog-Digital converters, Digital-          |     |

|        | Analog converters                            | 139 |

| 12.1   | Fundamental principles                       | 139 |

| 12.1.1 | General                                      | 139 |

| 12.1.2 | Analog-Digital converters                    | 139 |

| 12.1.3 | Digital-Analog converters                    | 140 |

| 12.2   | Experiments section                          | 141 |

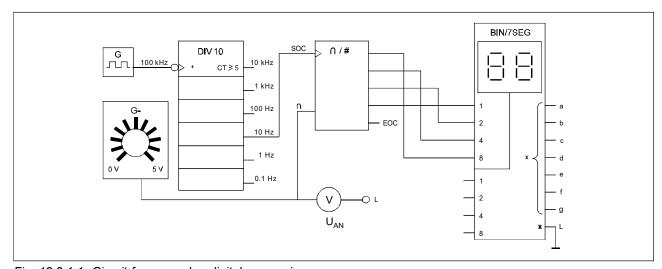

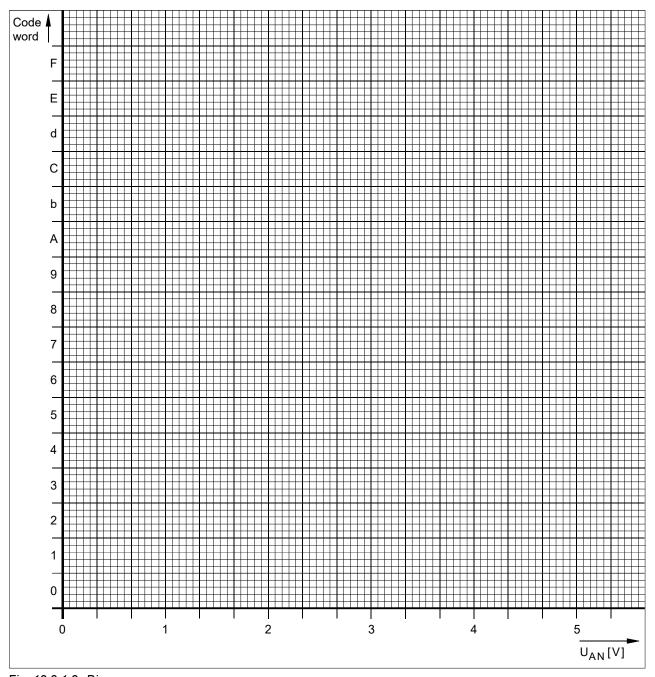

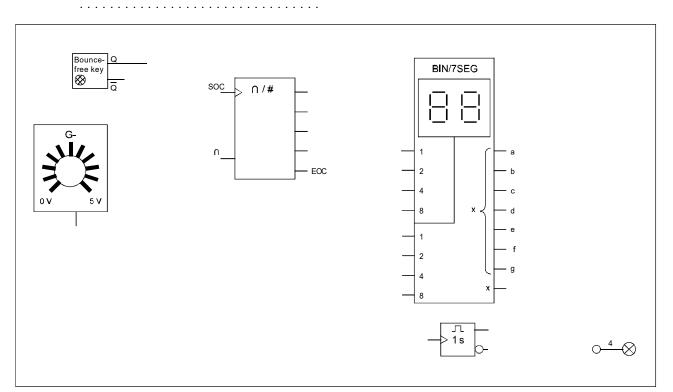

| 12.2.1 | Analog-Digital conversion                    | 141 |

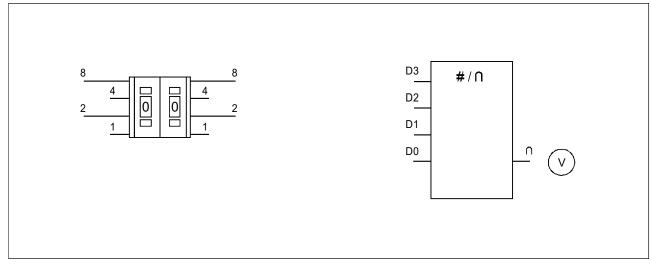

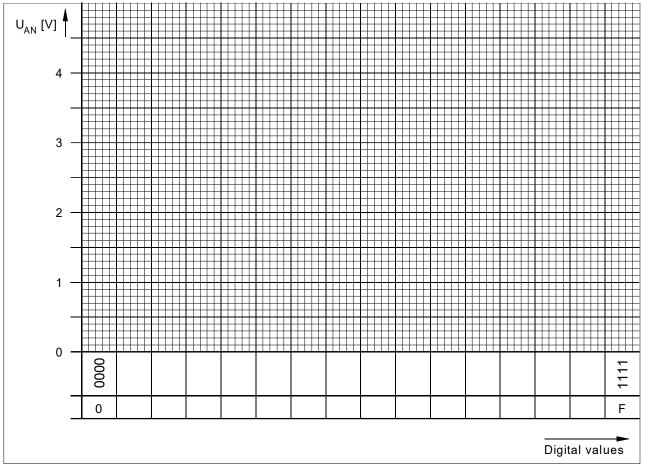

| 12.2.2 | Digital-Analog conversion                 |

|--------|-------------------------------------------|

| 12.2.3 | Signal transfer                           |

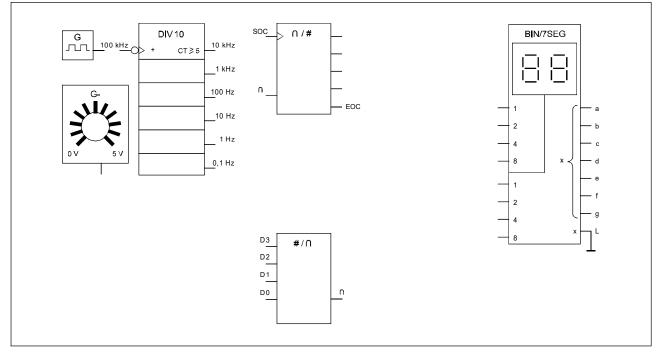

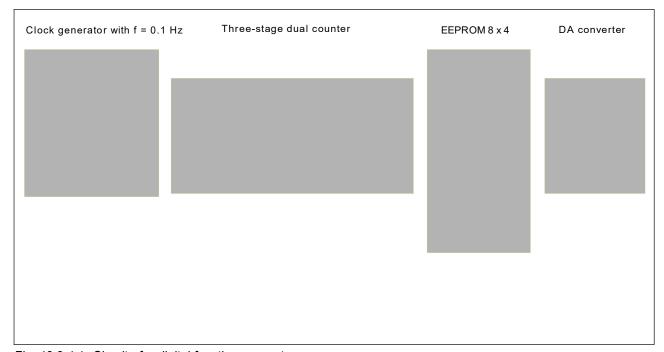

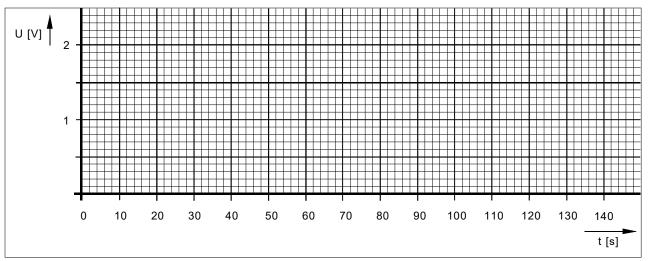

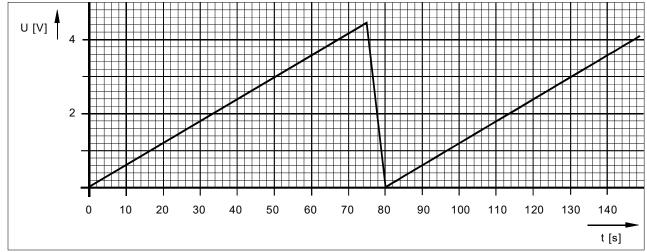

| 12.2.4 | Digital function generator                |

|        |                                           |

| Solut  | ions section S 1                          |

| 1.     | Basic logic circuits                      |

| 2.     | Schmitt triggers                          |

| 3.     | Bistable multivibrators                   |

| 4.     | Monostable multivibrators S 17            |

| 5.     | Code converters, coders S 19              |

| 6.     | Arithmetic circuits                       |

| 7.     | Counting circuits                         |

| 8.     | Register circuits                         |

| 9.     | Multiplex mode                            |

| 10.    | Arithmetic logic unit                     |

| 11.    | Memory circuits S 55                      |

| 12.    | Analog-Digital converters, Digital-Analog |

|        | converters S 59                           |

|        |                                           |

| Appe   | ndix A 1                                  |

| 1.     | List of symbols used in the formulae A 1  |

| 2.     | Measuring instruments used A 1            |

|        |                                           |

| Overl  | head foils F 1                            |

| DIGI B | SOARD 2                                   |

| DIGI M | MODULE BOARD F 2                          |

| Module | es F 3                                    |

## 1. Basic Logic Circuits

## 1.1 Fundamental Principles

#### 1.1.1 Forms of Representation and Aids

Electronic digital circuits are composed of basic eleements in which only two possible input and output signals need to be distinguished. These signals are represented either as a voltage level with the letters **H** (high) or **L** (low) or as a logic value with the values **0** and **1**.

Table 1.1.1.1 summarizes the possible designations of the input and output signals.

Positive logic is used for all the experiments in this manual.

The following forms of representation and aids are used to describe or comprehend the function of a single component or a digital circuit:

| Level | Logic value    |                |  |  |

|-------|----------------|----------------|--|--|

| Level | positive logic | negative logic |  |  |

| L     | 0              | 1              |  |  |

| Н     | 1              | 0              |  |  |

Tab. 1.1.1.1

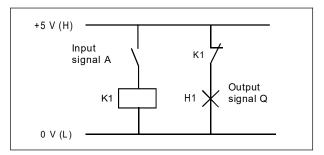

#### Circuit diagram/connection diagram:

Fig. 1.1.1.1 shows a circuit diagram or connection diagram with a NOT circuit with contacts as an example.

Fig. 1.1.1.1

#### Working table:

Table 1.1.1.2 shows the dependence of the output signals on the input signals as a level (L or H) with the NOT element as an example.

| Α | Q |

|---|---|

| L | Н |

| Н | L |

Table 1.1.1.2

#### Value table/truth table:

Table 1.1.1.3 shows the relationship between the input and output signals in the form of logic states (0 or 1) with the NOT element as an example.

| Α | Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

Table 1.1.1.3 Truth table

#### Function equation:

The function equation shows the relationship between the input and output signal as a formula. Linkage of single or several signals is represented by special symbols.

The form  $Q = A \cdot B$  is normally used because, firstly, it is very clear in connection with the symbols for the other switching functions and secondly because the truth table of a logic AND operation corresponds to the laws of arithmetic for multiplication of dual numbers and the form is permissible according to DIN.

## NOT element: $Q = \overline{A}$ (read A negated)

AND operation:

$$Q = A \wedge B$$

(read A and B) or

$$Q = A \cdot B = A B$$

OR operation:

$$Q = A \vee B$$

(read A or B)

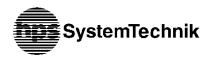

#### Logic plan:

A logic plan is the graphic representation of a digital circuit with circuit symbols.

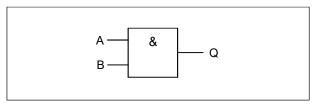

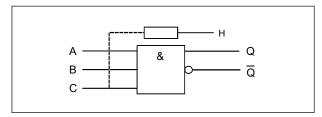

Fig. 1.1.1.2 shows the circuit symbol of the AND element with the two inputs A and B.

Fig. 1.1.1.2 Circuit symbol of an AND element

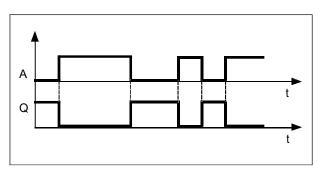

#### Timing diagram/pulse diagram:

A timing diagram or pulse diagram shows input and output signals of individual components or a digital circuit in relation to time.

Fig. 1.1.1.3 shows a timing diagram of a NOT element.

Fig. 1.1.1.3 Timing or pulse diagram

## 1.1.2 Laws of Switching Algebra

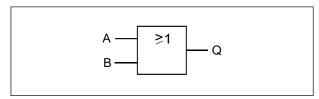

The logic operations AND, OR and NOT represent the three basic elements of digital logic. All simple control circuits can be described and set up with their help. If the output signal of an AND or OR element is negated this produces a NOT AND or NAND operation or NOT OR or NOR operation.

NAND and NOR elements have their own circuit symbols as they are used very frequently.

The following rules or laws must be observed for working with the basic functions and the switching algebra expressions:

Commutative laws:

(exchangeability of variables)

Associative laws:

(allocation of variables)

Distributive laws:

(distribution of variables)

Linkage laws:

These laws concern the linkage of a variable with itself (identities) or with a constant or with its negation (complement).

Absorption laws:

(bonding rules)

Double negation:

De Morgan laws:

(laws of reversal)

AB = BA and  $A \lor B = B \lor A$

A (B C) = (A B) C = (A C) B = A B C

$A \lor (B \lor C) = (A \lor B) \lor C = (A \lor C) \lor B = A \lor B \lor C$

$(A B) \lor (A C) = A (B \lor C)$

$(A \lor B) (A \lor C) = A \lor (B C)$

$A \wedge A = A$

$A \vee A = A$

$A \wedge 0 = 0$   $1 \wedge A = A$   $A \wedge \overline{A} = 0$

or or

or

$0 \lor A = A$  $1 \lor A = 1$  $A \vee \overline{A} = 1$

or

$A \wedge (A \vee B) = A$

$A \vee (A \wedge B) = A$

$\frac{\square}{A} = A$

$\overline{A \wedge B} = \overline{A} \vee \overline{B}$ and

$\overline{A \vee B} = \overline{A} \wedge \overline{B}$

#### 1.1.3 Complete Disjunctive Normal Form

There are two possible ways of deriving a switching network from a task posed in the form of a truth table, the complete disjunctive normal form and the complete conjunctive normal form.

The complete disjunctive normal form results when the **minterms** are noted for all combinations for which the output has the "1" state and these are linked by OR functions. A minterm is given by noting the AND operation of all switching variables and negating the variables which are in the "0" state in this combination.

Table 1.1.3.1 shows an example of the complete disjunctive normal form.

| Α | В                                                                  | С | Q | Minterms |  |

|---|--------------------------------------------------------------------|---|---|----------|--|

| 0 | 0                                                                  | 0 | 0 |          |  |

| 0 | 0                                                                  | 1 | 0 |          |  |

| 0 | 1                                                                  | 0 | 1 | ĀΒŒ      |  |

| 0 | 1                                                                  | 1 | 0 |          |  |

| 1 | 0                                                                  | 0 | 0 |          |  |

| 1 | 0                                                                  | 1 | 1 | ΑBC      |  |

| 1 | 1                                                                  | 0 | 0 |          |  |

| 1 | 1                                                                  | 1 | 1 | ABC      |  |

|   | $Q = \overline{A} B \overline{C} \vee A \overline{B} C \vee A B C$ |   |   |          |  |

Table 1.1.3.1

#### 1.1.4 Complete Conjunctive Normal Form

This results when the **maxterms** are noted for all combinations for which the output has the "0" state and these are linked by AND functions. A maxterm is given by noting the OR operation of all switching variables and negating the variables which are in the "1" state in this combination.

Table 1.1.4.1 shows an example of the complete conjunctive normal form.

The disjunctive or conjunctive normal forms taken from a value table are usually **redundant**, i. e. they contain superfluous components. The switching functions therefore need to be simplified. This minimization can be achieved arithmetically by applying the laws of switching algebra but it needs a lot of practice (see chapter 1.2.3, experiment 1, page 15).

Circuit minimization can be achieved faster and more reliably by a **KV diagram**, named after Karnaugh and Veitch. It is composed of chessboard-like fields, whereby the number of fields is equal to the number of signal combinations of the respective value table.

| Α                                                                                                                                | В | С | Z | Maxterms                                |  |

|----------------------------------------------------------------------------------------------------------------------------------|---|---|---|-----------------------------------------|--|

| 0                                                                                                                                | 0 | 0 | 1 |                                         |  |

| 0                                                                                                                                | 0 | 1 | 0 | $A \lor B \lor \overline{C}$            |  |

| 0                                                                                                                                | 1 | 0 | 1 |                                         |  |

| 0                                                                                                                                | 1 | 1 | 0 | $A \vee \overline{B} \vee \overline{C}$ |  |

| 1                                                                                                                                | 0 | 0 | 1 |                                         |  |

| 1                                                                                                                                | 0 | 1 | 1 |                                         |  |

| 1                                                                                                                                | 1 | 0 | 0 | $\overline{A} \vee \overline{B} \vee C$ |  |

| 1                                                                                                                                | 1 | 1 | 1 |                                         |  |

| $Z = (A \vee B \vee \overline{C}) \wedge (A \vee \overline{B} \vee \overline{C}) \wedge (\overline{A} \vee \overline{B} \vee C)$ |   |   |   |                                         |  |

Table 1.1.4.1

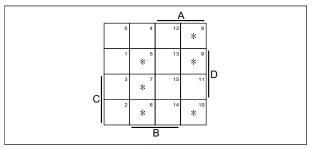

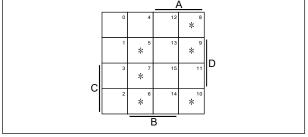

#### 1.1.5 KV Diagrams

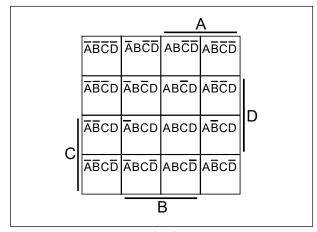

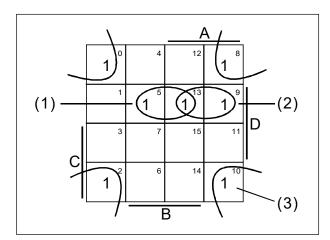

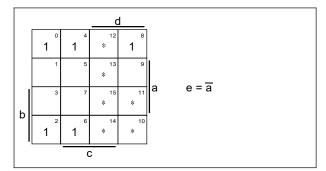

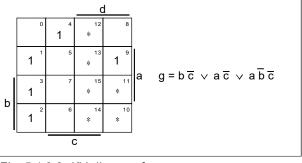

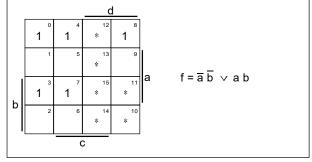

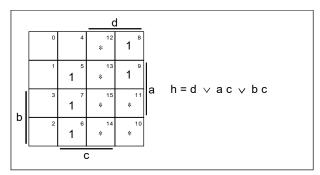

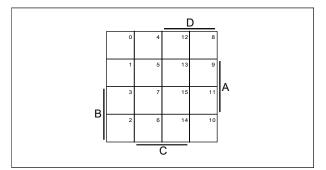

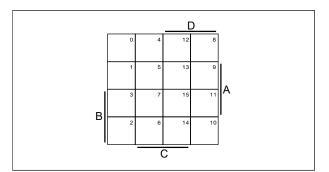

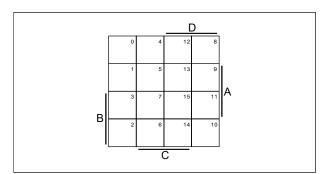

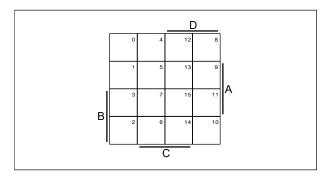

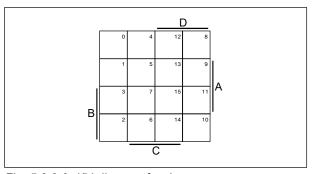

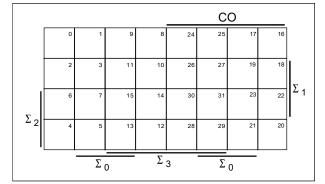

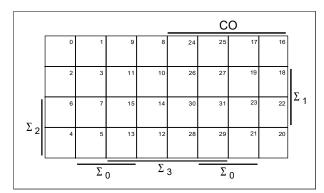

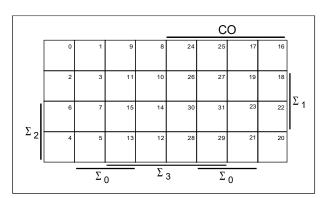

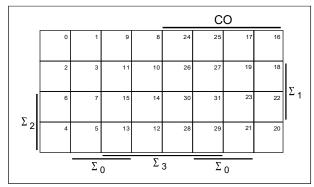

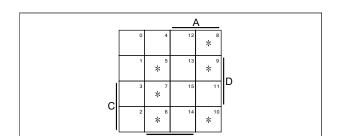

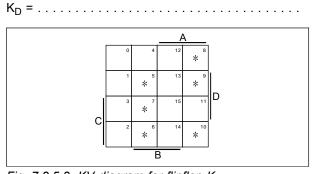

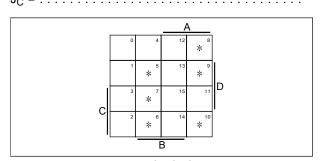

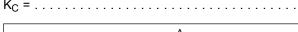

A KV diagram can be drawn in a number of different ways. To save yourself long derivation work it is advisable to decide on one version. The example in fig. 1.1.5.1 describes the locating of the minimum disjunctive normal form. This is a KV diagram for four input variables with  $A = 2^3$  (most significant bit).

The KV diagram contains all the minterms. These can be replaced by the corresponding dual numbers (fig. 1.1.5.2) for further simplification.

For application of the KV diagram the minterms are then read from the value table and transferred to the KV diagram.

The following should apply for the example in fig. 1.1.5.2:

$$Q = 0 \lor 2 \lor 5 \lor 8 \lor 9 \lor 10 \lor 13$$

Then adjacent fields occupied by "1" are combined in such a way that the combination has as many ones as possible.  $2^n$  (n = natural number) fields may be combined. The KV diagram in fig. 1.1.5.2 shows the three possible combinations.

The appropriate switching algebra expressions are obtained by combining the variables common to all fields in one logic AND operation.

The expressions for the combination are:

- (1)  $B\overline{C}D$

- (2)  $A \overline{C} D$

- (3)  $\overline{B}$   $\overline{D}$

The minimum switching function is therefore:

$$Q = B \overline{C} D \vee A \overline{C} D \vee \overline{B} \overline{D}$$

It now only has eight variables in comparison with the complete disjunctive normal form.

Fig. 1.1.5.1 KV diagram for four input variables

Fig. 1.1.5.2 Example

#### 1.1.6 Logic Functions with NOR and NAND Elements

Since modern integrated circuits can only be manufactured economically in large series, NAND and NOR elements are mainly manufactured in IS technology because they can be used for setting up any switching network. However, the problem of transforming the respective switching function into an expression which contains only NAND or NOR operations is now added to the problem of simplifying the switching functions.

The following laws of algebra offer the solution to this problem: De Morgan laws, double negation.

Since the form of writing with the help of NAND and NOR functions is very complicated, a switching network is developed by composing the switching functions from basic functions and minimizing them and only converting them into the desired logic operation in their final state.

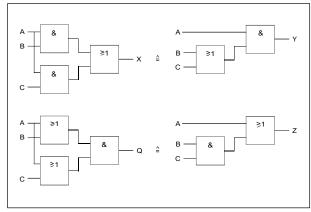

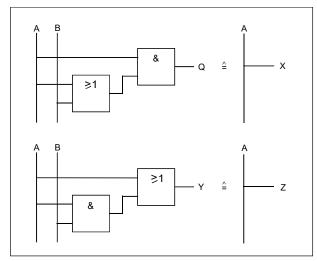

Fig. 1.1.6.1 shows a summary of the logic functions with NOR and NAND elements described above.

| Logic functions with |                                                                                                                                                                     |                                                                                                                                                                                 |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Basic elements       | NOR elements                                                                                                                                                        | NAND elements                                                                                                                                                                   |  |  |  |

| A — 1 0— Q           | A                                                                                                                                                                   | A & Q                                                                                                                                                                           |  |  |  |

| $Q = \overline{A}$   | $Q = \overline{A}$                                                                                                                                                  | Q = A                                                                                                                                                                           |  |  |  |

| A & Q                | A = 1                                                                                                                                                               | A & & 0 & & 0 - Q                                                                                                                                                               |  |  |  |

| Q = A ^ B            | $Q = A \wedge B$ $\overline{Q} = \overline{A \wedge B} = \overline{A} \vee \overline{B}$ $\overline{\overline{Q}} = Q = \overline{\overline{A} \vee \overline{B}}$  | $Q = A \wedge B$ $\overline{Q} = \overline{A \wedge B}$ $\overline{\overline{Q}} = Q = \overline{\overline{A \wedge B}}$                                                        |  |  |  |

| A                    | $A \longrightarrow \exists 1$ $B \longrightarrow \exists 1$ $Q = A \lor B$ $\overline{Q} = \overline{A \lor B}$ $\overline{\overline{Q}} = Q = \overline{A \lor B}$ | A $\otimes$ B $\otimes$ Q = A $\vee$ B $\overline{Q} = \overline{A} \vee \overline{B} = \overline{A} \wedge \overline{B}$ $\overline{Q} = Q = \overline{A} \wedge \overline{B}$ |  |  |  |

Fig. 1.1.6.1

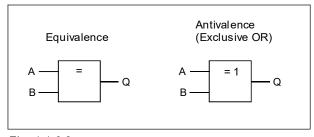

When linking two switching variables A and B, the **equivalence** and **antivalence** are also important in addition to the NOR and NAND operation (fig. 1.1.6.2).

In equivalence, the output always has "1" state when both inputs have the same level. Equivalence elements are used above all in comparator circuits.

The antivalence always supplies a "1" to the output when both inputs have opposite levels. Antivalence elements are used partly in logic circuits (semi adder, semi subtractor) because their value table corresponds to the rules of arithmetic for two dual numbers (without taking the carry into account).

Fig. 1.1.6.2

## 1.2 Experiments Section

## 1.2.1 Important Binary Logic Operations

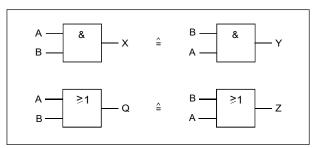

## ☐ Experiment 1: Fundamental principles

#### **Experiment procedure:**

- Examine the circuit symbols shown in fig. 1.2.1.1 and fill in the missing data.

- Write the name of the circuit beneath each circuit symbol.

| Circuit symbol  | Value table             | Circuits with contacts | Function equation |

|-----------------|-------------------------|------------------------|-------------------|

| A — 1 0— Q      | A Q 0 1 1               |                        |                   |

| A — & B — Q     | A B Q 0 0 0 0 1 1 0 1 1 |                        |                   |

| A — ≥1<br>B — Q | A B Q 0 0 0 0 1 1 0 1 1 |                        |                   |

| A — & o— Q      | A B Q 0 0 0 0 1 1 0 1 1 |                        |                   |

| A — ≥1          | A B Q 0 0 0 0 1 1 0 1 1 |                        |                   |

Fig. 1.2.1.1

## 1.2.2 Laws of Switching Algebra

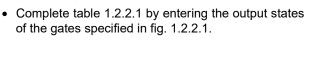

#### ☐ Experiment 1: The commutative laws

Make sure that the commutative laws are correct.

#### **Experiment procedure:**

#### N. B.:

The order need **not** be observed when assigning AND and OR inputs.

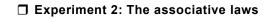

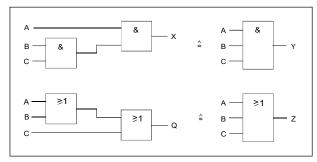

Make sure that the associative laws are correct.

#### **Experiment procedure:**

• Complete table 1.2.2.2 by entering the output states of the gates specified in fig. 1.2.2.2.

For AND and OR circuits **one** gate with **many** inputs can be made up of **several** gates with **few** inputs.

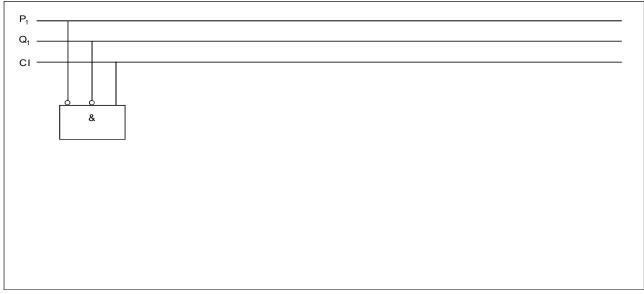

Fig. 1.2.2.1

|   |   | AND |   | 0 | R |

|---|---|-----|---|---|---|

| Α | В | х   | Υ | Q | Z |

| 0 | 0 |     |   |   |   |

| 0 | 1 |     |   |   |   |

| 1 | 0 |     |   |   |   |

| 1 | 1 |     |   |   |   |

Table 1.2.2.1 Truth table

Fig. 1.2.2.2

|   |   |   | A | ND | 0 | R |

|---|---|---|---|----|---|---|

| Α | В | С | Х | Y  | Q | Z |

| 0 | 0 | 0 |   |    |   |   |

| 0 | 0 | 1 |   |    |   |   |

| 0 | 1 | 0 |   |    |   |   |

| 0 | 1 | 1 |   |    |   |   |

| 1 | 0 | 0 |   |    |   |   |

| 1 | 0 | 1 |   |    |   |   |

| 1 | 1 | 0 |   |    |   |   |

| 1 | 1 | 1 |   |    |   |   |

Table 1.2.2.2 Truth table

#### ☐ Experiment 3: The distributive laws

Make sure that the distributive laws are correct.

#### **Experiment procedure:**

• Complete table 1.2.2.3 by entering the output states of the circuits specified in fig. 1.2.2.3.

Fig. 1.2.2.3

#### N. B.:

If AND and OR terms combined by an OR or AND operation contain the **same** variable, this can be **factored out** as a common factor in mathematics. This saves gates.

| Α | В | С | Х | Υ | Q | Z |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 |   |   |   |   |

| 0 | 0 | 1 |   |   |   |   |

| 0 | 1 | 0 |   |   |   |   |

| 0 | 1 | 1 |   |   |   |   |

| 1 | 0 | 0 |   |   |   |   |

| 1 | 0 | 1 |   |   |   |   |

| 1 | 1 | 0 |   |   |   |   |

| 1 | 1 | 1 |   |   |   |   |

Table 1.2.2.3 Truth table

#### Notes:

#### ☐ Experiment 4: Possible combinations of a switching variable

Check the possible combinations of a switching variable for identity, as a complement or as a constant.

#### **Experiment procedure:**

Complete the tables 1.2.2.4 and 1.2.2.5 by entering the respective output state of the gate in fig. 1.2.2.4 and 1.2.2.5 once as a logic value and once as variable A or constant.

If an AND circuit has more inputs than are required, the inputs which are not needed can either be combined with the **required** inputs or applied to the level corresponding to **value 1**.

Fig. 1.2.2.4

|   |   | Q as        | Q as variable A |

|---|---|-------------|-----------------|

| Α | В | logic value | or constant     |

| 0 | 0 |             |                 |

| 1 | 1 |             |                 |

| 0 | 0 |             |                 |

| 1 | 0 |             |                 |

| 0 | 1 |             |                 |

| 1 | 1 |             |                 |

| 0 | 1 |             |                 |

| 1 | 0 |             |                 |

Table 1.2.2.4 Truth table

Fig. 1.2.2.5

|   |   | Q as        | Q as variable A |

|---|---|-------------|-----------------|

| Α | В | logic value | or constant     |

| 0 | 0 |             |                 |

| 1 | 1 |             |                 |

| 0 | 0 |             |                 |

| 1 | 0 |             |                 |

| 0 | 1 |             |                 |

| 1 | 1 |             |                 |

| 0 | 1 |             |                 |

| 1 | 0 |             |                 |

Table 1.2.2.5 Truth table

#### N. B.:

In an OR circuit, extra inputs must be combined with **used** inputs or applied to the level corresponding to **value 0**.

#### ☐ Experiment 5: Absorption laws

Make sure that the absorption laws are correct.

#### **Experiment procedure:**

• Complete the table 1.2.2.6 by entering the output states of the circuits specified in fig. 1.2.2.6 once as a logic value and once as a variable.

#### N. B.:

If OR and AND terms are linked by a common variable AND or OR, the output has the value of the **common** variable. This makes the circuit less complicated.

Fig. 1.2.2.6

|   |   |   | Logic |   |   |          |

|---|---|---|-------|---|---|----------|

| Α | В | Q | Х     | Υ | Z | variable |

| 0 | 0 |   |       |   |   |          |

| 0 | 1 |   |       |   |   |          |

| 1 | 0 |   |       |   |   |          |

| 1 | 1 |   |       |   |   |          |

Table 1.2.2.6 Truth table

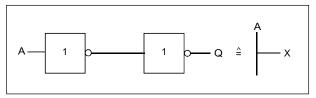

#### ☐ Experiment 6: Double negation

Check the law of double negation.

#### **Experiment procedure:**

• Complete the table 1.2.2.7 by entering the output states of the circuits specified in fig. 1.2.2.7.

Fig. 1.2.2.7

#### N. B.:

In digital circuits it is sometimes necessary to bridge the signal propagation times of certain gates or to amplify a signal. Inverters are suitable for this because the signal returns to its **original** state after the second inverter.

| Α | q | x |

|---|---|---|

| 0 |   |   |

| 1 |   |   |

Table 1.2.2.7

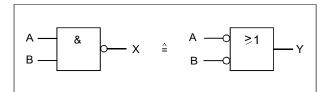

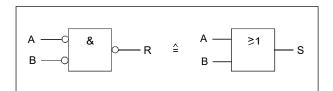

#### ☐ Experiment 7: De Morgan laws

Check the De Morgan laws.

#### **Experiment procedure:**

• Complete the tables 1.2.2.8 ... 1.2.2.11 by entering the output states of the circuits specified in figs. 1.2.2.8 ... 1.2.2.11.

Fig. 1.2.2.8

| Α | В | X | Υ |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

Table 1.2.2.8

Fig. 1.2.2.10

| Α | В | R | S |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

Table 1.2.2.10

#### N. B.:

The De Morgan laws offer the possibility of setting up circuits with **NAND** or **NOR** gates only.

Fig. 1.2.2.9

| Α | В | Q | Z |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

Table 1.2.2.9

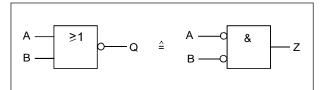

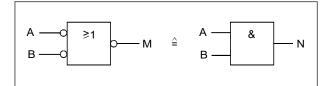

Fig. 1.2.2.11

| Α | В | М | N |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

Table 1.2.2.11

#### 1.2.3 Disjunctive and Conjunctive Normal Form

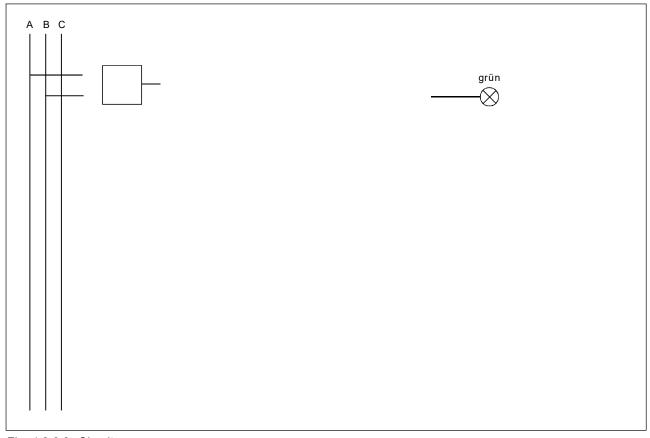

#### ☐ Experiment 1: Controlling an electric network

A current network must be optically controlled to avoid overloading by built-in heating units. The three sets A, B and C have the rated powers 4 kW, 6 kW and 8 kW. If the power taken from the network exceeds 11 kW a yellow warning lamp should light up, if it exceeds 13 kW a red warning lamp should light up. A green lamp signals safe operation.

#

Fig. 1.2.3.1 Input keyboard

#### **Experiment procedure:**

- Complete the table 1.2.3.1 with binary numbers.

- Then design the switching functions for driving the lamps with the aid of the truth table and simplify these functions with the laws of the switching algebra.

- Complete the circuit in fig. 1.2.3.2 (page 16) and check its function with the Digital Training System.

- Note: Fig. 1.2.3.1 shows how the outputs of the input keyboard can be allocated to the input variables of a circuit.

Green (conjunctive normal form):

| 4 kW | 6 kW | 8 kW | P [kW]  | W     | arning lar | np  |

|------|------|------|---------|-------|------------|-----|

| Α    | В    | С    | F [KVV] | green | yellow     | red |

| 0    | 0    | 0    |         |       |            |     |

| 0    | 0    | 1    |         |       |            |     |

| 0    | 1    | 0    |         |       |            |     |

| 0    | 1    | 1    |         |       |            |     |

| 1    | 0    | 0    |         |       |            |     |

| 1    | 0    | 1    |         |       |            |     |

| 1    | 1    | 0    |         |       |            |     |

| 1    | 1    | 1    |         |       |            |     |

Table 1.2.3.1 Value table

Yellow (disjunctive normal form):

| ,                       |                                |

|-------------------------|--------------------------------|

| x =                     | Y =                            |

|                         |                                |

|                         |                                |

|                         | Yellow (simplified): Y =       |

|                         | Red (disjunctive normal form): |

| Green (simplified): X = | Z =                            |

|                         | Red (simplified): Z =          |

Fig. 1.2.3.2 Circuit

## Notes:

#### 1.2.4 Circuit Design with the Aid of KV Diagrams

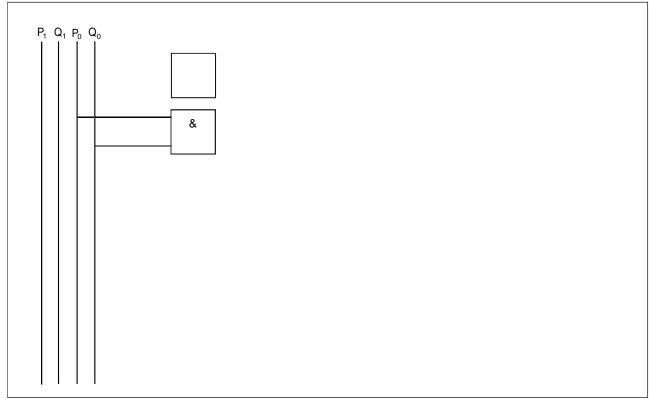

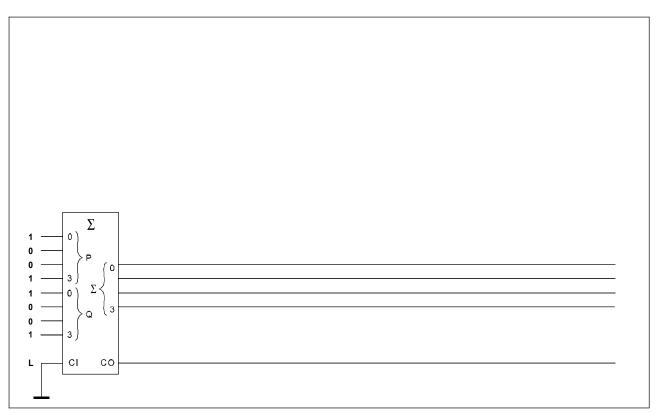

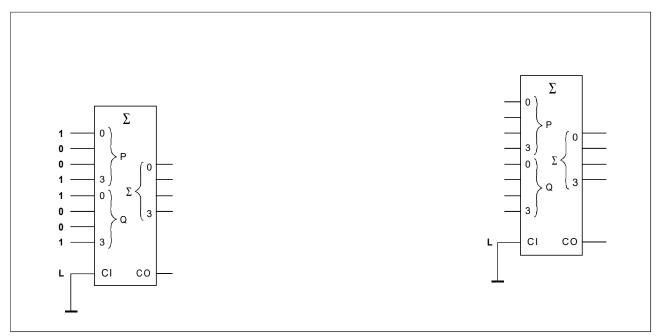

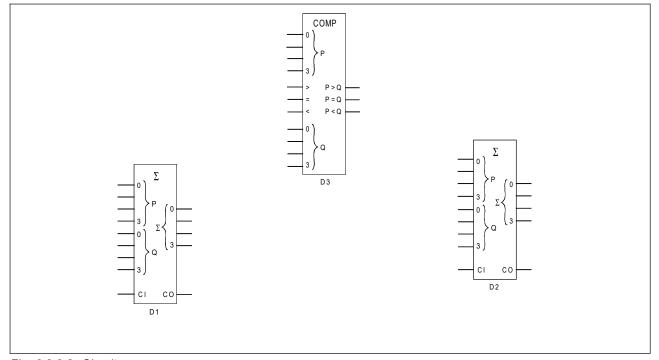

#### ☐ Experiment 1: Number comparator for dual numbers

A digital circuit with which two dual numbers can be checked for equality or inequality is known as a number comparator.

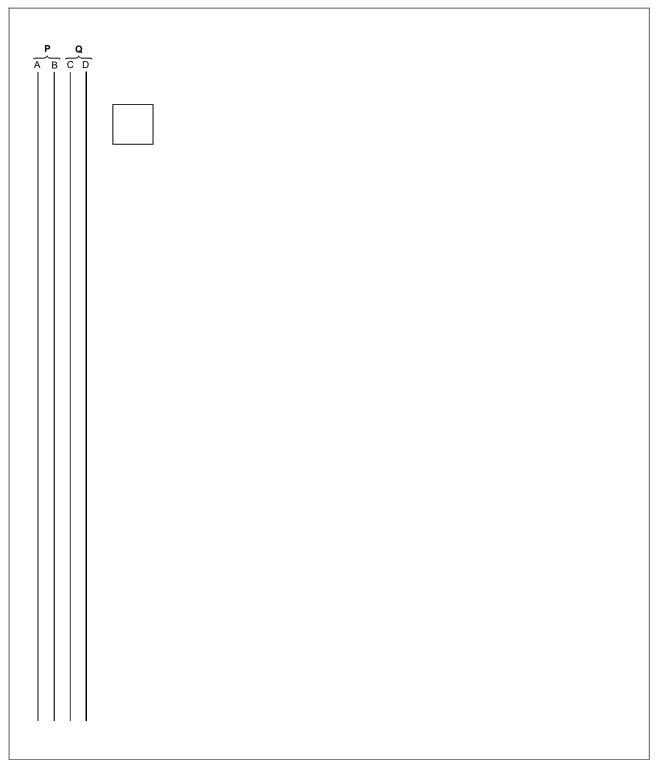

In this experiment, a circuit is to be designed which is able to compare two dual numbers P and Q with two bits each. A greater-smaller comparison should also be carried out in the event of inequality.

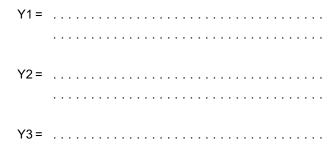

#### **Experiment procedure:**

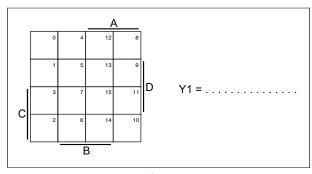

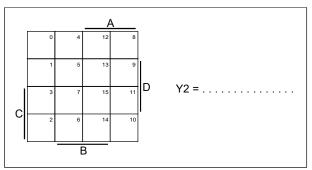

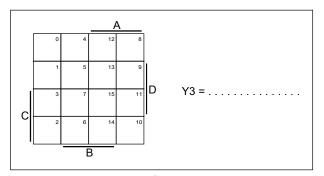

- Complete table 1.2.4.1 and design the three function equations Y1, Y2 and Y3 (complete disjunctive normal form) with the aid of the truth table.

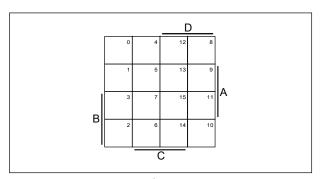

- Minimize the three function equations with the aid of the KV diagrams (figs. 1.2.4.1 ... 1.2.4.3).

- Complete the circuit in fig. 1.2.4.4 (page 18) and check its function with the Digital Training System.

|     | Inp   | uts |       |     | Outputs |       |

|-----|-------|-----|-------|-----|---------|-------|

| Num | ber P | Num | ber Q | P>Q | P = Q   | P < Q |

| Α   | В     | С   | D     | Y1  | Y2      | Y3    |

| 0   | 0     | 0   | 0     |     |         |       |

| 0   | 0     | 0   | 1     |     |         |       |

| 0   | 0     | 1   | 0     |     |         |       |

| 0   | 0     | 1   | 1     |     |         |       |

| 0   | 1     | 0   | 0     |     |         |       |

| 0   | 1     | 0   | 1     |     |         |       |

| 0   | 1     | 1   | 0     |     |         |       |

| 0   | 1     | 1   | 1     |     |         |       |

| 1   | 0     | 0   | 0     |     |         |       |

| 1   | 0     | 0   | 1     |     |         |       |

| 1   | 0     | 1   | 0     |     |         |       |

| 1   | 0     | 1   | 1     |     |         |       |

| 1   | 1     | 0   | 0     |     |         |       |

| 1   | 1     | 0   | 1     |     |         |       |

| 1   | 1     | 1   | 0     |     |         |       |

| 1   | 1     | 1   | 1     |     |         |       |

Table 1.2.4.1 Truth table

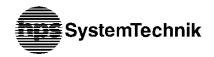

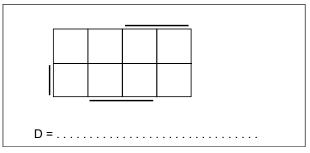

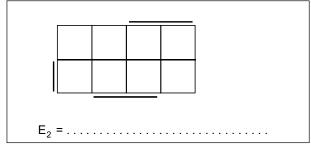

Fig. 1.2.4.1 KV diagram for Y1

Fig. 1.2.4.2 KV diagram for Y2

Fig. 1.2.4.3 KV diagram for Y3

Fig. 1.2.4.4 Circuit of a number comparator for dual numbers

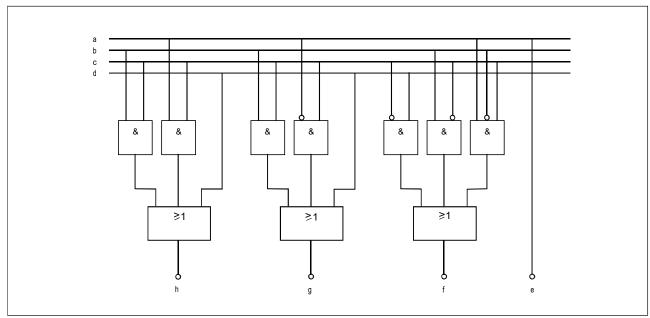

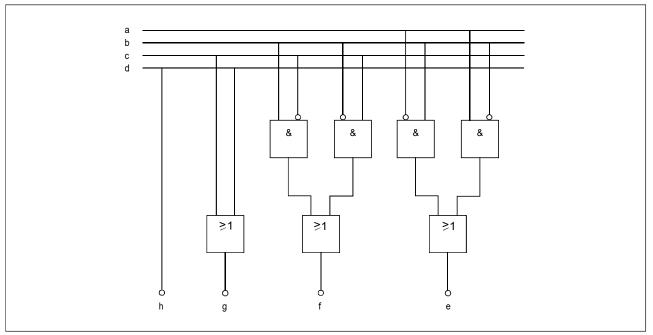

#### 1.2.5 Representation of Switching Networks in NAND or NOR Technology

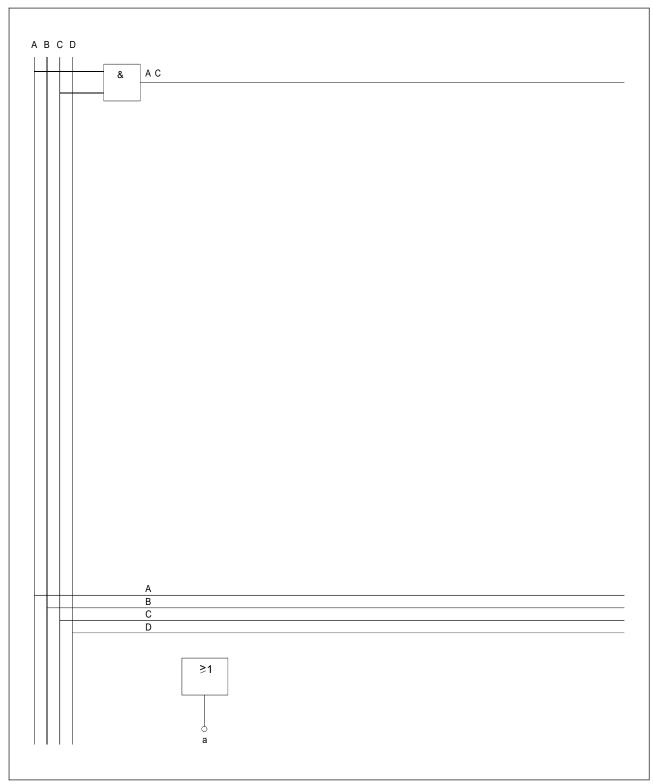

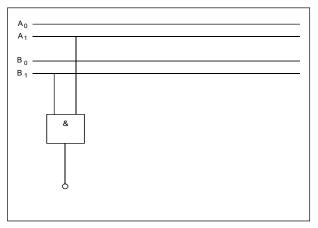

#### ☐ Experiment 1: Pseudo-tetrade monitoring

For tetradic codes (e. g. 8421-BCD code), a decimal number is converted into a 4-digit binary number (tetrade). Sixteen different combinations can be represented with one tetrade of which only 10 combinations are required. The combinations which cannot be assigned to decimal numbers are referred to as **pseudotetrades**.

In the experiment, a circuit is to be designed which produces a 1-signal at output Q when a pseudo-tetrade is applied to the inputs (pseudo-tetrade monitoring).

#### **Experiment procedure:**

- Complete table 1.2.5.1.

- Determine the disjunctive normal form with the aid of the value table and minimise with the laws of the switching algebra.

- Complete the circuit in fig. 1.2.5.1 and check its function with the Digital Training System.

| Decimal |       | Dual n | umber |                            | Q |  |  |  |  |  |  |  |  |  |  |

|---------|-------|--------|-------|----------------------------|---|--|--|--|--|--|--|--|--|--|--|

| number  | A (8) | B (4)  | C (2) | D (1)                      | " |  |  |  |  |  |  |  |  |  |  |

| 0       | 0     | 0      | 0     | 0                          |   |  |  |  |  |  |  |  |  |  |  |

| 1       | 0     | 0      | 0     | 1                          |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       |                            |   |  |  |  |  |  |  |  |  |  |  |

|         |       |        |       | Table 4.0.5.4. Value table |   |  |  |  |  |  |  |  |  |  |  |

Table 1.2.5.1 Value table

| Q = | = |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-----|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|     |   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     |   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     |   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     |   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Q = | = |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

Fig. 1.2.5.1 Circuit

| <ul> <li>Experiment procedure:</li> <li>Convert the circuit in fig. 1.2.5.1 so that it now only consists of NAND gates and complete fig. 1.2.5.2.</li> </ul> | Question<br>lation met | <b>1:</b> Can NAND gates be saved with the calcuthod? |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------|

| <ul> <li>Then do the conversion in fig. 1.2.5.2 by calculation.</li> </ul>                                                                                   | Answer:                |                                                       |

| Test the circuit with the Digital Training System.                                                                                                           |                        |                                                       |

| Q =                                                                                                                                                          |                        |                                                       |

| <u>Q</u> =                                                                                                                                                   |                        |                                                       |

| <u></u>                                                                                                                                                      |                        |                                                       |

|                                                                                                                                                              |                        |                                                       |

|                                                                                                                                                              |                        |                                                       |

| A B C D                                                                                                                                                      |                        |                                                       |

Fig. 1.2.5.2 Circuit in NAND technology

| ☐ Experiment 3: NOR technology                                                                                                                          |                  |                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------|

| <ul> <li>Experiment procedure:</li> <li>Convert the circuit in fig. 1.2.5.1 so that it consists of NOR gates only and complete fig. 1.2.5.3.</li> </ul> |                  | 1: Compare experiments 2 and 3. Which equires the most effort? |

| • Do the conversion in fig. 1.2.5.3 by calculation.                                                                                                     | Answer:          |                                                                |

| Test the circuit with the Digital Training System.                                                                                                      |                  |                                                                |

| Q =                                                                                                                                                     |                  |                                                                |

| <u> </u>                                                                                                                                                | Question method? | 2: Can NOR gates be saved by the calculation                   |

| Q =                                                                                                                                                     | Answer:          |                                                                |

|                                                                                                                                                         |                  |                                                                |

|                                                                                                                                                         |                  |                                                                |

| A B C D                                                                                                                                                 |                  |                                                                |

Fig. 1.2.5.3 Circuit in NOR technology

| 1.2.6 Equivalence                                                                                                                                                      |                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| ☐ Experiment 1: Fundamental principles                                                                                                                                 |                             |

| Examine the circuit for equivalence.                                                                                                                                   |                             |

| <ul><li>Experiment procedure:</li><li>Draw the symbol for the switching function in fig. 1.2.6.1.</li></ul>                                                            |                             |

| <ul> <li>Complete table 1.2.6.1 with the aid of fig. 1.2.6.1 and<br/>specify the disjunctive normal form.</li> </ul>                                                   | Fig. 1.2.6.1 Circuit symbol |

| Q =                                                                                                                                                                    | Table 1.2.6.1 Value table   |

| ☐ Experiment 2: 1-bit number comparator                                                                                                                                | Table 1.2.6.1 Value table   |

| Design the circuit of a 1-bit number comparator in which a greater-smaller comparison is also carried out in addition to equality of two 1-digit dual numbers P and Q. | P                           |

| Experiment procedure:                                                                                                                                                  |                             |

| <ul> <li>Complete table 1.2.6.2 and determine the disjunctive<br/>normal forms for P &gt; Q, P = Q and P &lt; Q.</li> </ul>                                            | Table 1.2.6.2 Value table   |

| Draw the circuit in fig. 1.2.6.2 and check its function with the Digital Training System.                                                                              |                             |

| P > Q:                                                                                                                                                                 |                             |

| P = Q:                                                                                                                                                                 |                             |

| P < Q:                                                                                                                                                                 |                             |

Fig. 1.2.6.2 Circuit

#### 1.2.7 Antivalence

#### ☐ Experiment 1: Fundamental principles

#### **Experiment procedure:**

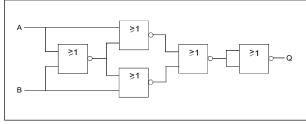

- Complete the value table (table 1.2.7.1) for the circuit shown in fig. 1.2.7.1.

- Draw the circuit in fig. 1.2.7.1 as a circuit symbol (fig. 1.2.7.2) and convert it to the disjunctive normal form using the laws of switching algebra.

Fig. 1.2.7.1

| Q = |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Q = |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

Table 1.2.7.1 Value table

Fig. 1.2.7.2 Circuit symbol

**Question 1:** The logic of our circuit corresponds to a lamp circuit familiar from installation technology. Name it and draw the connection diagram as confirmation (fig. 1.2.7.3).

| Answer:  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| AIISWEI. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

Fig. 1.2.7.3 Connection diagram

#### 1.2.8 Working with TTL Components

#### ☐ Experiment 1: AND/NAND gates with pull-up resistor

TTL means Transistor-Transistor Logic. In this circuit family, the logic operations are generated exclusively by bipolar transistor systems.

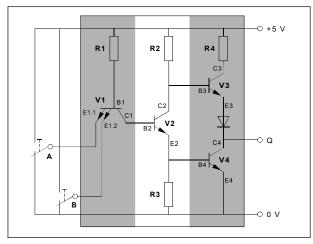

Fig. 1.2.8.1 shows the principle structure of a NAND gate of the standard TTL series 74.

The circuit consists of a multi-emitter transistor V1 which carries out an AND linkage of the input signals. The series-connected inverter, consisting of the transistors V2, V3 and V4 reverses the input signal.

Note: The NAND or AND gate is already used in chapter 1.2.4.

#### **Experiment procedure:**

- Describe the function of the circuit in fig. 1.2.8.1 by completing table 1.2.8.1.

- Note: B E: base-emitter line, B C: base-collector line

- Then check the AND/NAND gate with the Digital Training System by completing table 1.2.8.2.

- Note: Use the connection through the pull-up resistor for the H-level at input C.

If the 2 mm connecting plug is not plugged in, the inputs are not connected and faults may occur because there is no defined state.

Unconnected inputs of TTL gates behave in the same way as inputs connected to **H level**.

Fig. 1.2.8.1 NAND gate in TTL technology

| Inp | uts | Transi | stor V1 | V2         | V3 | V4 | Outp. |

|-----|-----|--------|---------|------------|----|----|-------|

| Α   | В   | B-E    | B-C     | <b>V</b> 2 | •• | •  | Q     |

| L   | L   |        |         |            |    |    |       |

| L   | Н   |        |         |            |    |    |       |

| Н   | L   |        |         |            |    |    |       |

| Н   | Н   |        |         |            |    |    |       |

Table 1.2.8.1

Fig. 1.2.8.2 NAND gate with pull-up resistor

|   | Inputs |      | Q for | Q for |

|---|--------|------|-------|-------|

| Α | В      | С    | AND   | NAND  |

| L | L      | open |       |       |

| L | L      | Н    |       |       |

| Н | Н      | open |       |       |

| Н | Н      | Н    |       |       |

Table 1.2.8.2

#### ☐ Experiment 2: OR/NOR gates with pull-down resistor

#### **Experiment procedure:**

- Check the OR/NOR gate (fig. 1.2.8.3) with the Digital Training System.

- Complete table 1.2.8.3.

- **Note:** Use the connection through the pull-down resistor for the L level at input C.

|   | Inputs | Q for<br>OR | Q for<br>NOR |     |

|---|--------|-------------|--------------|-----|

| Α | В      | С           | OR           | NOR |

| L | L      | open        |              |     |

| L | L      | L           |              |     |

| Н | Н      | open        |              |     |

| Н | Н      | L           |              |     |

Table 1.2.8.3

#### N.B:

Unused inputs of an AND or NAND gate are effective because they already have H level. In practice it is usual to **apply unused inputs** of a gate to **H level**.

This can only be achieved in an OR or NOR gate, however, if the unused inputs are applied to **L level**.

Fig. 1.2.8.3

#### Notes:

Notes:

## 2. Schmitt Triggers

## 2.1 Fundamental Principles

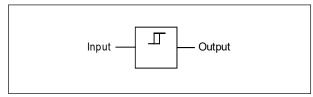

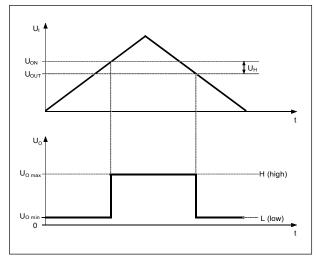

A Schmitt trigger or **threshold switch** is a controllable multivibrator with two stable switching states. The Schmitt trigger forms a squarewave output voltage  $U_{\rm O}$  from a continuously changing input voltage  $U_{\rm I}$ .

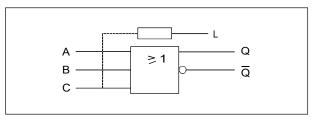

Fig. 2.1.1 shows the circuit symbol of a Schmitt trigger. The input of the Schmitt trigger does **not** carry a binary signal.

Fig. 2.1.1 Circuit symbol of a Schmitt trigger

The switching state resident at the output of the Schmitt trigger depends on the value of the voltage applied to the control input.

Fig. 2.1.2 shows that the trigger process is activated at the Schmitt trigger input when the **threshold voltage**  $U_{ON}$  is exceeded and the output voltage  $U_{O\,max}$  remains at its maximum value until the input voltage reaches and falls below the value of the **return voltage U\_{OFF}**. The difference between these two input voltages is referred to as the **hysteresis U\_H**.

$U_H = U_{ON} - U_{OFF}$

Fig. 2.1.2 Voltages of the Schmitt trigger

## 2.2 Experiments Section

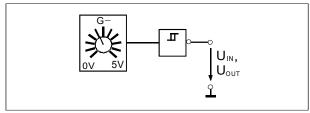

#### ☐ Experiment 1: Inverting Schmitt trigger

#### **Experiment procedure:**

- Set up the circuit as shown in fig. 2.2.1.

- Measure the threshold voltage U<sub>ON</sub> and the return voltage U<sub>OFF</sub> with an analog voltmeter by turning the potentiometer slowly to the right (U<sub>ON</sub>) and then slowly to the left (U<sub>OFF</sub>) and noting the respective last readable voltage value before the jump.

- Determine the hysteresis U<sub>H</sub> and then complete the diagram in fig. 2.2.2.

| U <sub>ON</sub>  | = | - |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|------------------|---|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| U <sub>OFF</sub> | = |   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| U <sub>H</sub>   | = |   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

**Question 1:** Which logic gate can be used to replace this Schmitt trigger if necessary?

| Answer: |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|---------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

**Question 2:** How does the circuit in fig. 2.2.1 need to be completed in order to produce a Schmitt trigger whose output voltage adopts the upper value on exceeding the on threshold and the lower value on falling below the off threshold?

Fig. 2.2.1 Circuit

Fig. 2.2.2

## 3. Bistable Multivibrators

## 2.1 Fundamental Principles

#### 3.1.1 General

When processing signals, it is frequently necessary to retain the signal states beyond the time that the signals are applied and to put them into effect later. So-called sequential digital circuits have such signal memories in addition to **non-storing** logic elements, e. g. AND, OR, NOT elements.

The value of the output variable of such a circuit therefore depends not only on the values of the input variables but also on the states of the signal memories at the same time.

Signal memories are formed by a bistable multivibrator (flipflop) which can store the information of one bit.

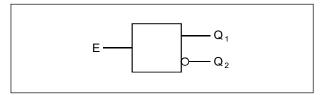

The basic component for all flipflops in digital technology is the **RS flipflop**. The number of inputs may be different but every flipflop has exactly two outputs which carry complementary (opposite) levels. Equal output states may not occur by way of definition even if this is partially possible.

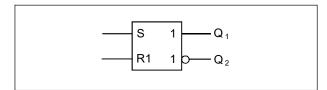

#### 3.1.2 Asynchronous Flipflops

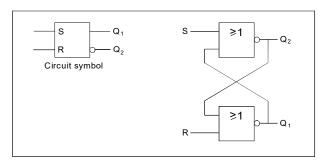

In the circuit symbol the inputs are identified according to their function by **Set** or **S** and **Reset** or **R**. The complementary output levels are represented with the inversion of the  $Q_2$  output.

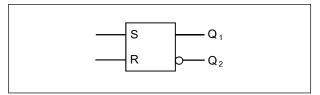

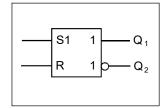

Fig. 3.1.2.1 shows the circuit symbol of an RS flipflop with non-inverting inputs.

- State ",1" at S switches the flipflop to Q<sub>1</sub> = 1 (set)

- State "1" at R switches the flipflop to Q<sub>2</sub> = 1 (reset)

- The "0" states have no controlling effect here.

Fig. 3.1.2.1 Circuit symbol of an RS flipflop

29

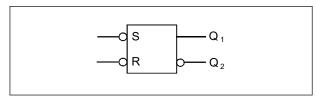

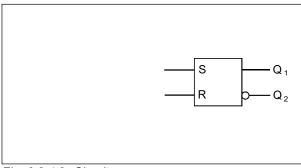

RS flipflops which are controlled by 0 states have special inputs characterized by a negation circuit (fig. 3.1.2.2).

- State "0" at S switches the flipflop to Q<sub>1</sub> = 1 (set).

- State "0" at R switches the flipflop to Q<sub>2</sub> = 1 (reset).

- The "1" states have no controlling effect here.

Flipflops usually have a fixed basic setting. After applying the supply voltage the flipflop is in the so-called **quiescent state** with  $Q_1 = 0$  and  $Q_2 = 1$ .

Flipflops which adopt the operating state  $\mathbf{Q_1} = \mathbf{1}$  and  $\mathbf{Q_2} = \mathbf{0}$  after switching on the supply voltage are shown in fig. 3.1.2.3.

· The flipflop is set after switching on.

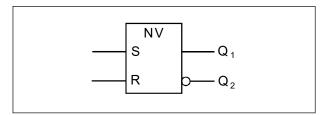

If a flipflop does **not** lose the stored information in the event of a loss of voltage, **NV** (non-volatile) is entered in the circuit symbol (fig. 3.1.2.4).

• The flipflop has the same logic state it had when switching off after switching on the supply voltage.

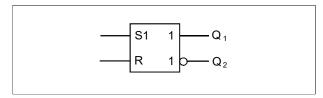

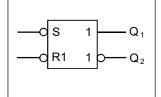

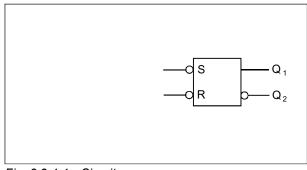

A considerable disadvantage of the RS flipflop is its irregular state in the case of High level at S and R. In most flipflops, this state combination is prohibited because equal output levels  $Q_1 = Q_2 = 0$  occur. By means of additional circuit measures (chapter 3.2.4, experiments 1 and 2, page 34) the flipflop can be set or reset **dominant** (with priority) instead (fig. 3.1.2.5 and 3.1.2.6).

- Dominant S input: The flipflop is set when S = R = 1

- Dominant R input: The flipflop is reset when S = R = 1

The flipflops dealt with above are referred to as asynchronous flipflops because they operate without a clock signal and can be set at any time by input signals.

Fig. 3.1.2.2 RS flipflop with inverting inputs

Fig. 3.1.2.3

Fig. 3.1.2.4 NV-RS flipflop

Fig. 3.1.2.5 RS-FF with dominant S-input

Fig. 3.1.2.6 RS-FF with dominant R input

## 3.1.3 Synchronous Flipflops

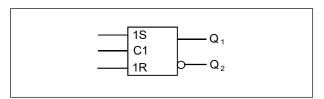

Flipflops which are controlled by a clock are known as synchronous flipflops. They have an input known as the clock input in addition to the set and reset inputs.

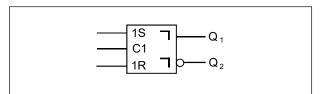

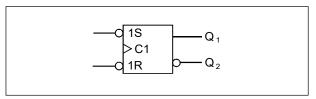

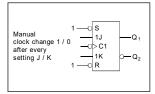

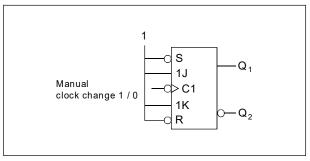

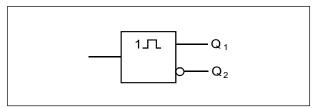

Fig. 3.1.3.1 shows the circuit symbol for a **one state controlled RS flipflop**.

The set and reset inputs are only effective if there is a 1-signal at the clock input C1.

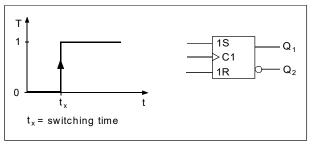

Since this flipflop with its static clock input can be set or reset unintentional by an interference pulse throughout the whole clock pulse time, it is better to use a **dynamic** clock input.

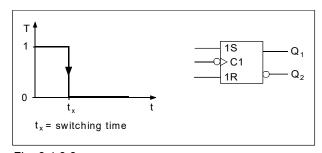

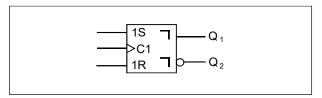

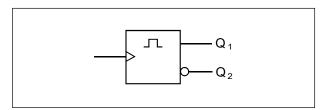

A flipflop with a dynamic clock input is known as a **single edge controlled RS flipflop** (fig. 3.1.3.2 and 3.1.3.3).

- The flipflop in fig. 3.1.3.2 can only be set or reset with a rising (positive) clock edge.

- The flipflop in fig. 3.1.3.3 can only be set or reset with a falling (negative) clock edge.

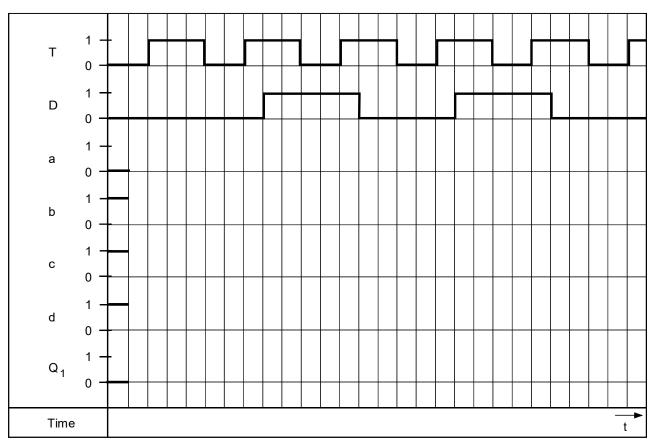

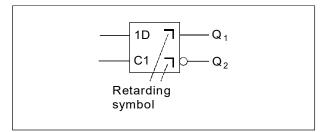

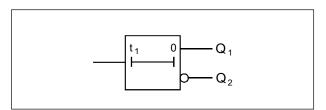

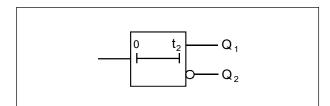

In some application circuits with flipflops such as counters and shift registers, there must be a difference in time between the signal input and the signal output. Flipflops with **signal buffering** are therefore used. The buffer may act **statically** (fig. 3.1.3.4) or **dynamically** (fig. 3.1.3.5).

- The input information is recorded during the one clock state and output until the following clock state (fig. 3.1.3.4).

- The input information is read in during the one clock edge and only passed on with the following edge (fig. 3.1.3.5).

Fig. 3.1.3.1 One state controlled RS flipflop

Fig. 3.1.3.2 Single edge controlled RS flipflop

Fig. 3.1.3.3

Fig. 3.1.3.4 Two state controlled RS flipflop

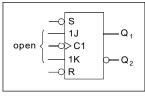

Fig. 3.1.3.5 Two edge controlled RS flipflop

With a suitable external wiring, the disadvantage common to all RS flipflops of equal output levels at a certain input level combination can be prevented. This results in flipflops as shown in fig. 3.1.3.6 ... 3.1.3.8 independently of the clock control used.

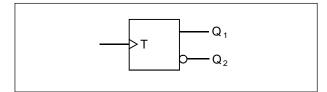

- The T flipflop triggers at every controlling clock edge.

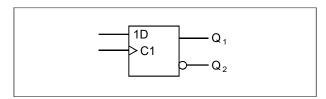

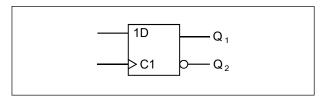

- The D flipflop stores the state at D with the controlling edge and passes it on to Q<sub>1</sub>.

- The JK flipflop records the input signal with rising clock edge and outputs it at Q<sub>1</sub> with the falling clock edge.

The switching behaviour of a flipflop can be described with the aid of a working table.

Since flipflops are very often used in sequential (timedependent) circuits, however, their behaviour is usually represented in the form of timing diagrams.

Fig. 3.1.3.6 T flipflop

Fig. 3.1.3.7 D flipflop

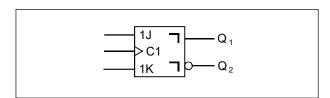

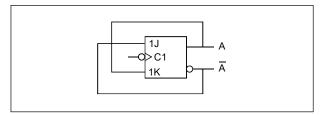

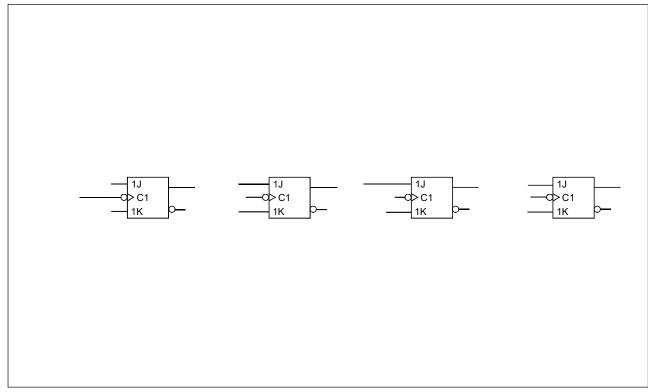

Fig. 3.1.3.8 JK flipflop

# 3.2 Experiments Section

#### 3.2.1 RS Flipflop consisting of NOR Gates

#### ☐ Experiment 1: Fundamental principles

Examine the RS flipflop in fig. 3.2.1.1.

#### **Experiment procedure:**

- Set up the circuit shown in fig. 3.2.1.1.

- Apply the values specified in table 3.2.1.1 one after the other to the inputs S and R of the circuit and fill in the missing output values for Q<sub>1</sub> and Q<sub>2</sub>.

- Explain the behaviour of the flipflop in table 3.2.1.1 with the terms set, reset, store, not defined (stored output state is random if S and R change from H to L at the same time) and irregular (Q<sub>1</sub> and Q<sub>2</sub> have no opposite levels).

33

Fig. 3.2.1.1 Circuit

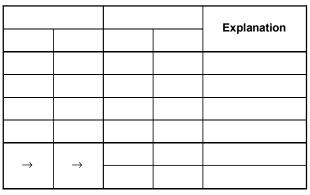

| S     | R      | Q <sub>1</sub> | Q <sub>2</sub> | Explanation |

|-------|--------|----------------|----------------|-------------|

| 0     | 0      | 0              | 1              | Store       |

| 1     | 0      | 1              | 0              | Set         |

| 0     | 0      | 1              | 0              | Store       |

| 0     | 1      |                |                |             |

| 0     | 0      |                |                |             |

| 1     | 1      |                |                |             |

| 1 → 0 | 1 → 0  | 0              | 1              |             |

|       | 1 -7 0 | 1              | 0              |             |

Table 3.2.1.1 Value table

# ☐ Experiment 2: Simplified form

In practice, only a simplified form is normally used instead of the detailed value table.

At the time  $\mathbf{t_n}$ , the values are applied to the inputs of the binary memory. The time  $\mathbf{t_{n+1}}$  follows the time tn. The state of the flipflop at time  $\mathbf{t_n}$  is therefore described by  $\mathbf{q_n}$ .

The flipflop may be in the set or reset state at the time  $t_n$ . The state of the flipflop complementary to  $q_n$  at the time  $t_n$  is  $\overline{q}_n$ .

# **Experiment procedure:**

• Complete the table 3.2.1.2.

Table 3.2.1.2

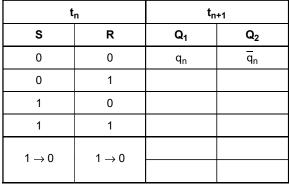

## 3.2.2 RS Flipflop consisting of NAND Gates

#### ☐ Experiment 1: Fundamental principles

Examine the RS flipflop in fig. 3.2.2.1.

#### **Experiment procedure:**

- Set up the circuit shown in fig. 3.2.2.1.

- Complete the table 3.2.2.1.

Fig. 3.2.2.1 Circuit

| t     | n      | t <sub>n</sub> | +1             | Explanation |

|-------|--------|----------------|----------------|-------------|

| s     | R      | Q <sub>1</sub> | Q <sub>2</sub> | Explanation |

| 0     | 0      |                |                |             |

| 0     | 1      |                |                |             |

| 1     | 0      |                |                |             |

| 1     | 1      |                |                |             |

| 0 → 1 | 0 → 1  |                |                |             |

|       | 0 -> 1 |                |                |             |

Table 3.2.2.1

#### ☐ Experiment 2: SR memory flipflop

If a NOT gate is connected before every input of the circuit in fig. 3.2.2.1, an SR memory flipflop is obtained. Characterize the behaviour of the SR memory flipflop.

#### **Experiment procedure:**

- Set up the circuit as shown in fig. 3.2.2.1 and insert a NOT gate in front of the inputs S and R.

- Complete the table 3.2.2.2.

#### N.B:

Since the SR memory flipflop behaves like an **RS flipflop consisting of NOR gates** when setting and resetting, it also has the same circuit symbol.

Table 3.2.2.2

# 3.2.3 Clock State Controlled RS Flipflops

#### ☐ Experiment 1: One state controlled RS flipflop

In many cases it is undesirable for the output state of the flipflop to change even only a few nanoseconds after the input state changes. Clock state controlled RS flipflops were developed for this reason.

#### **Experiment procedure:**

- Set up the circuit as shown in fig. 3.2.3.1. The clock is treated here as a third binary input.

- Complete the table 3.2.3.1 and the pulse diagram in fig. 3.2.3.2.

#### N. B.:

The pulse diagram in fig. 3.2.3.2 shows the disadvantage of one state controlled clock inputs. After the clock, the state of the flipflop corresponds to the **last** information at the end of the clock. The probability of errors as a result of this can be kept low if a **small** enough clock duration is selected.

Fig. 3.2.3.1 Circuit

| Clock T | s | R | Q <sub>1</sub> | Q <sub>2</sub> | Explanation |

|---------|---|---|----------------|----------------|-------------|

| 0       | 0 | 0 |                |                |             |

| 0       | 1 | 0 |                |                |             |

| 0       | 0 | 1 |                |                |             |

| 0       | 1 | 1 |                |                |             |

| 1       | 0 | 0 |                |                |             |

| 1       | 1 | 0 |                |                |             |

| 1       | 0 | 1 |                |                |             |

| 1       | 1 | 1 |                |                |             |

Table 3.2.3.1

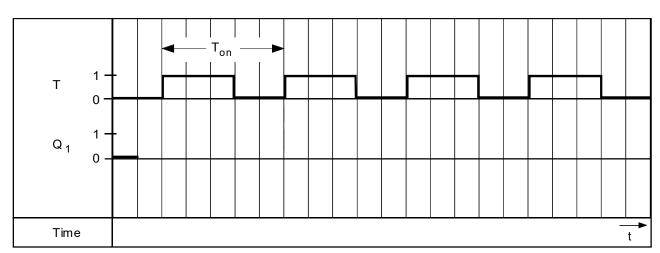

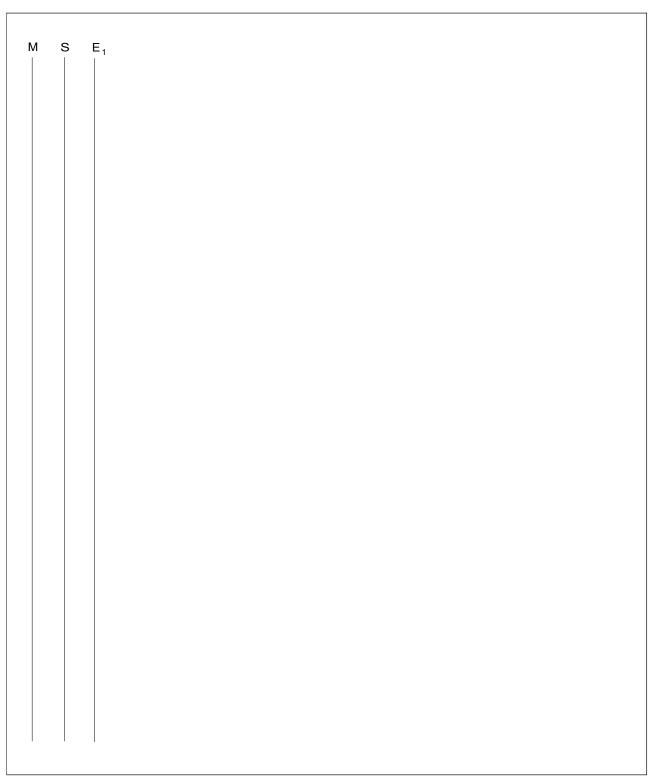

Fig. 3.2.3.2 Pulse diagram of the one state controlled RS flipflop

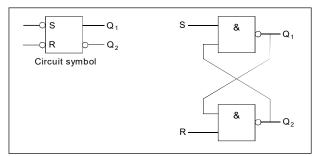

#### 3.2.4 RS Flipflops with Dominant S or R Input

#### ☐ Experiment 1: RS flipflop with dominant S input

The irregular case of the RS flipflop prompts the following consideration: Could you not construct a flipflop which always sets  $Q_1$  to 1 at S=1 and R=1? Design an input wiring which makes this possible.

The circuit symbol (fig. 3.2.4.1) and the value table (table 3.2.4.1) show an RS flipflop which fulfills this condition.

| S | R | $Q_1$          | $Q_2$            |

|---|---|----------------|------------------|

| 0 | 0 | q <sub>n</sub> | $\overline{q}_n$ |

| 0 | 1 | 0              | 1                |

| 1 | 0 | 1              | 0                |

| 1 | 1 | 1              | 0                |

Fig. 3.2.4.1

Table 3.2.4.1

#### **Experiment procedure:**

- Complete fig. 3.2.4.2 with an additional wiring.

- Then check the circuit with the Digital Training System.

- Note: Use the outputs Q of the input keyboard for inputs R and S because the JK flipflop of the Digital Training System has negated inputs.

Fig. 3.2.4.2 Circuit

#### ☐ Experiment 2: RS flipflop with dominant R input

An RS flipflop which must be reset at S=0 and R=0 ( $Q_1=0$ ) would also be conceivable. Design the appropriate input wiring.

The circuit symbol (fig. 3.2.4.3) and the value table (table 3.2.4.2) show an RS flipflop which fulfills this condition.

| S | R | Q <sub>1</sub> | Q <sub>2</sub>   |

|---|---|----------------|------------------|

| 0 | 0 | 0              | 1                |

| 0 | 1 | 1              | 0                |

| 1 | 0 | 0              | 1                |

| 1 | 1 | q <sub>n</sub> | $\overline{q}_n$ |

Fig. 3.2.4.3

Table 3.2.4.2

# Experiment procedure:

- Complete fig. 3.2.4.4 with an additional wiring.

- Then check the circuit with the Digital Training System.

Fig. 3.2.4.4 Circuit

#### 3.2.5 D Flipflops

#### ☐ Experiment 1: Fundamental principles

Flipflops with one state controlled clock inputs are often used as binary memory components. They are then usually designed as D flipflops.

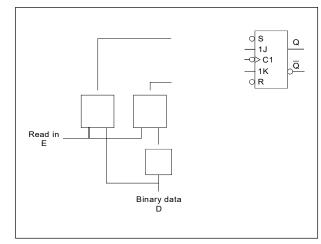

Examine the D flipflop in fig. 3.2.5.1.

#

Fig. 3.2.5.1 Circuit symbol

#### **Experiment procedure:**

- Set up the circuit as shown in fig. 3.2.5.1.

- Examine the function by completing the value table (table 3.2.5.1).

| Clock T | D | Q <sub>1</sub> | Q <sub>2</sub> |

|---------|---|----------------|----------------|

| 1       | 0 |                |                |

| 1       | 1 |                |                |

Table 3.2.5.1

#### ☐ Experiment 2:

As far as its function is concerned, the D flipflop with state controlled clock input can be considered as a corresponding RS flipflop in which only permissible switching states exist.

Set up this circuit. Only NAND gates are available.

#### Experiment procedure:

- Complete the circuit in fig. 3.2.5.2 and then enter the levels for transferring a "0" or a "1" into the circuit.

- Check the circuit with the Digital Training System.

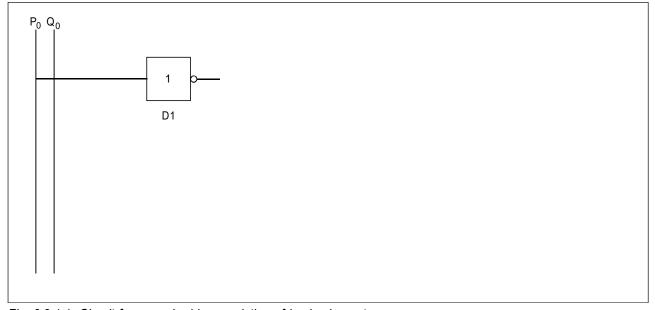

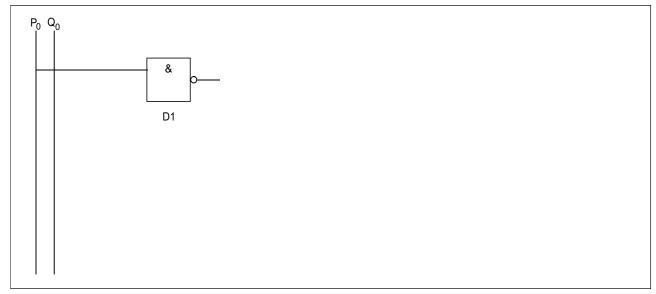

# & O—Q<sub>1</sub> D4 & O—Q<sub>2</sub> D5

Fig. 3.2.5.2 Circuit

#### N. B.:

This flipflop only has permissible switching states because only a NAND element can have 0 state at the input. This guarantees that the state required for switching can only occur at either D4 or D5.

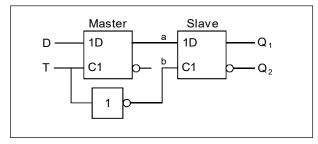

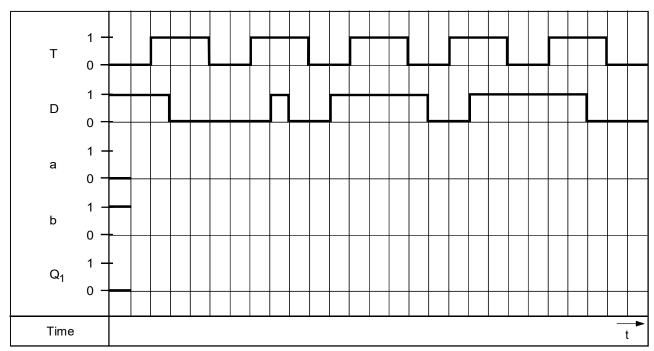

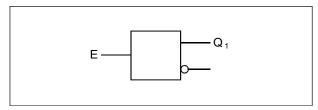

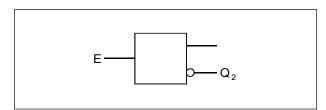

## 3.2.6 Single Edge Controlled RS Flipflop

#### ☐ Experiment 1: Fundamental principles

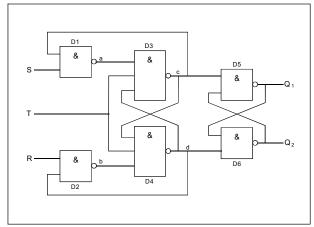

The susceptibility to disturbance of the clock state controlled RS flipflop (see chapter 3.2.3, page 35) can be further reduced if setting or resetting of a flipflop is only possible during the edge of the clock pulse.

Technically the edge control can be realized with a CR circuit and a diode for inhibiting the negative or positive needle pulses (differentiator).

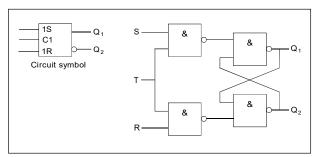

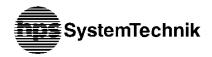

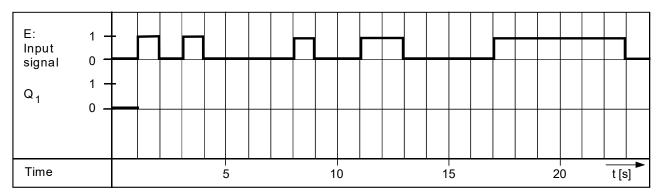

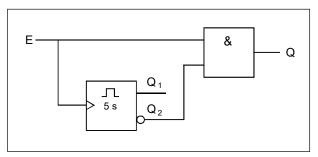

Fig. 3.2.6.1 shows the circuit symbol and fig. 3.2.6.2 the circuit for the principle of a singled edge controlled RS flipflop without using a differentiator.

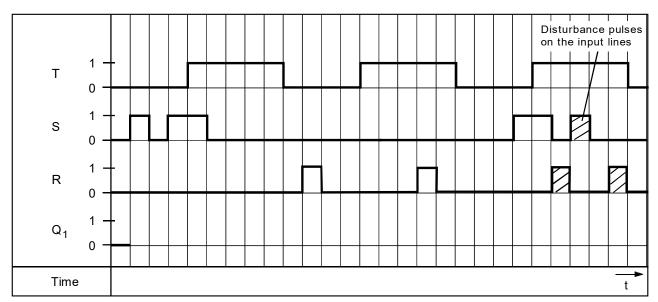

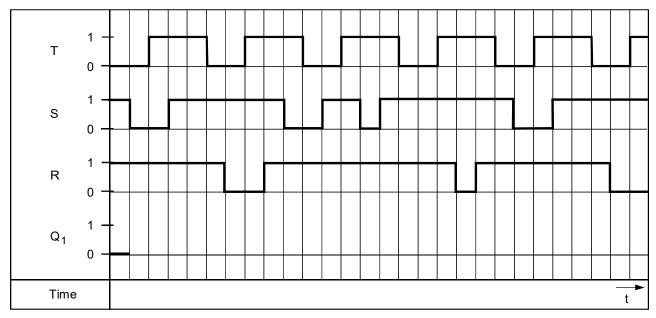

#### **Experiment procedure:**

38

- Set up the circuit as shown in fig. 3.2.6.2.

- Check the function of the circuit with the Digital Training System and complete the pulse diagram in fig. 3.2.6.3.

V 0160

Fig. 3.2.6.1 Circuit symbol

Fig. 3.2.6.2 Circuit

Fig. 3.2.6.3 Pulse diagram of the single edge controlled RS flipflop

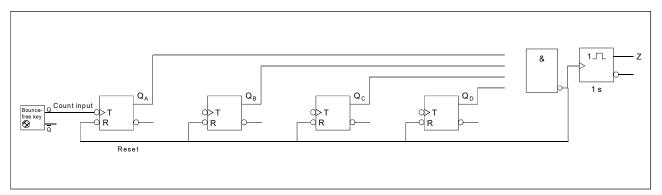

| that the fl<br>the clock,<br>Test this | 1: The pulse diagram in fig. 3.2.6.3 shows ipflop can also change its output state during i. e. no obvious inhibiting effect exists. with the circuit in fig. 3.2.6.2. Connect outputs d d to LEDs for this. Describe what happens. | if the buff<br>diately aft<br>Which lev | 2: The clock edge control therefore only works for (D3 and D4) inhibits its own inputs immedier accepting the signal.  Yels would therefore have to be applied to and d for the triggering edge? |